SSI

EPS2U Power Supply Design Guide, V2.1

8.2 PWOK (Power OK)

STATUS

Required

PWOK is a power OK signal and will be pulled HIGH by the power supply to indicate that all the outputs are within

the regulation limits of the power supply. When any output voltage falls below regulation limits or when AC power

has been removed for a time sufficiently long so that power supply operation is no longer guaranteed, PWOK will

be deasserted to a LOW state. See Figure 3 for a representation of the timing characteristics of PWOK. The

start of the PWOK delay time shall be inhibited as long as any power supply output is in current limit.

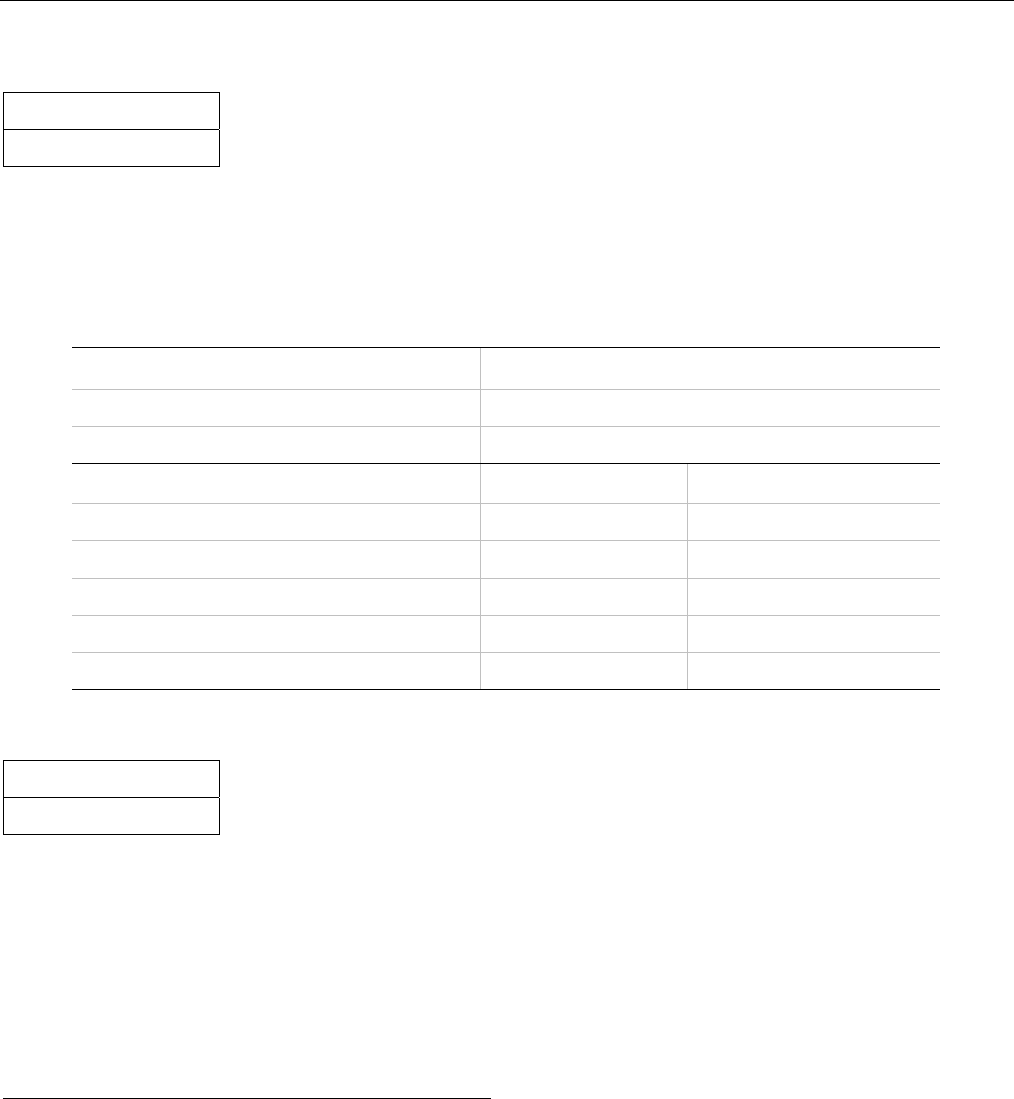

Table 29: PWOK Signal Characteristics

Signal Type

+5V TTL Compatible output signal

PWOK = High

Power OK

PWOK = Low

Power Not OK

MIN MAX

Logic level low voltage, Isink = 4 mA

0 V 0.4 V

Logic level high voltage, Isource=200 µA

2.4 V 5.25 V

PWOK delay: T

pwok_on

200 ms 1000 ms

PWOK rise and fall time

100 µs

Power down delay: T

pwok_off

1 ms 200 ms

8.3 Field Replacement Unit (FRU) Signals

STATUS

Optional

Two pins will be allocated for the FRU information on the power supply connector. One pin is the Serial Clock

(SCL). The second pin is used for Serial Data (SDA). Both pins are bi-directional and are used to form a serial

bus. The FRU circuits inside the power supply must be powered off of 5 VSB output and grounded to ReturnS

(remote sense return). The Write Control (or Write protect) pin should be tied to ReturnS inside the power supply

so that information can be written to the EEPROM.

8.3.1 FRU Data

FRU data shall be stored starting in address location 8000h through 80FFh. The FRU data format shall be

compliant with the IPMI specifications. The current versions of these specifications are available at:

http:\\developer.intel.com/design/servers/ipmi/spec.htm

.

- 27 -