Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

SMSC LAN9420/LAN9420i 111 Revision 1.22 (09-25-08)

DATASHEET

4.3.7 DMA Controller Control (Operation Mode) Register (DMAC_CONTROL)

This register establishes the RX and TX operating modes and commands. This should be the last

DCSR written as part of initialization.

Offset: 0018h Size: 32 bits

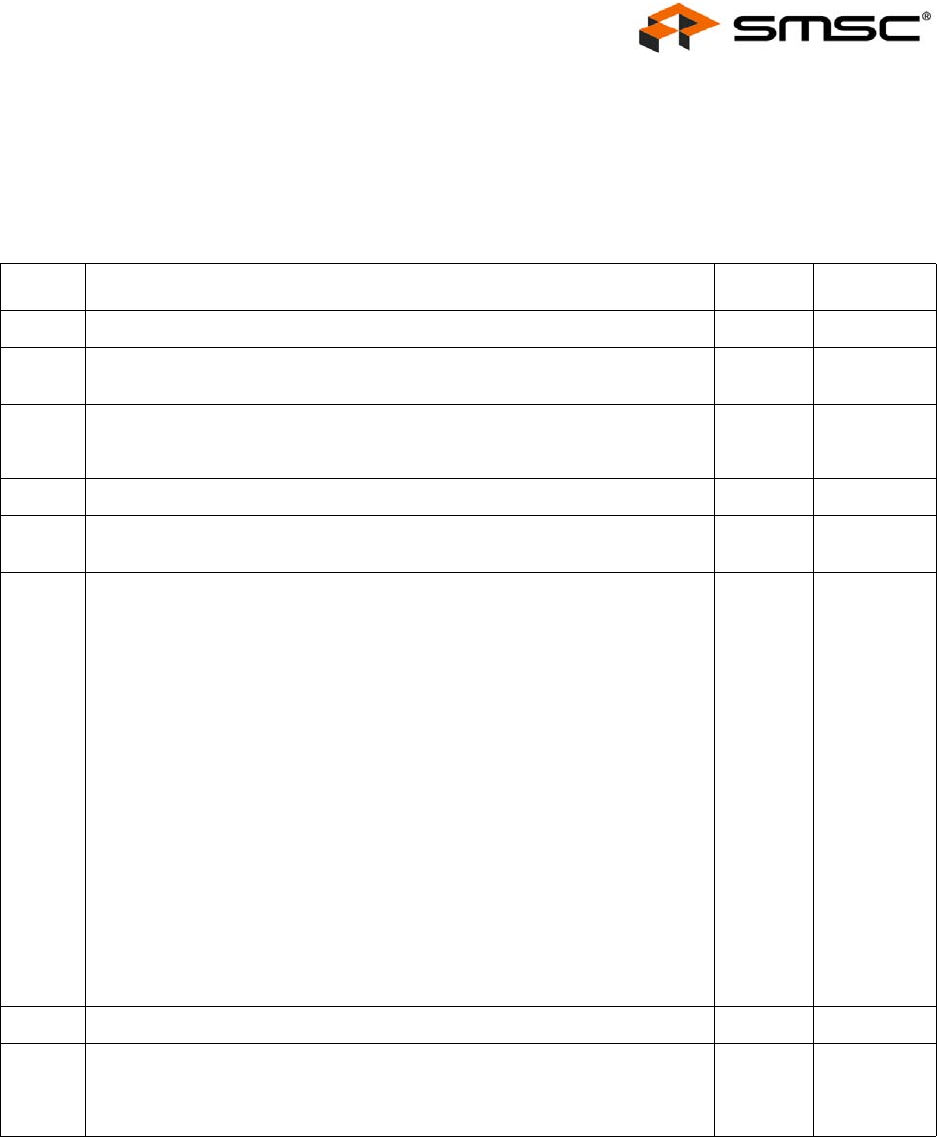

BITS DESCRIPTION TYPE DEFAULT

31:23 RESERVED RO -

22 RESERVED

R/W 0b

21 Must Be One (MBO)

This bit must be set to ‘1’ for normal device operation.

R/W 0b

19:16 RESERVED RO -

15:14 RESERVED R/W 00b

13 Start/Stop Transmission Command (ST)

When set, the transmission process is placed in the Running state, and the

DMAC checks the transmit list at the current position for a frame to be

transmitted.

Descriptor acquisition is attempted either from the current position in the list,

which is the transmit list base address set by TX_BASE_ADDR, or from the

position retained when the transmit process was previously stopped. If no

descriptor can be acquired, the transmit process enters the Suspended

state. If the current descriptor is not owned by the DMA Controller, the

transmission process enters the Suspended state and the Transmit Buffer

Unavailable (DMAC_STATUS bit [2]) is set. The Start Transmission

command is effective only when the transmission process is stopped. If the

command is issued before setting the TX_BASE_ADDR, then the DMA

Controller’s behavior will be undefined.

When reset, the transmission process is placed in the Stopped state after

completing the transmission of the current frame. The next descriptor

position in the transmit list is saved, and becomes the current position when

transmission is restarted.

The Stop Transmission command is effective only when the transmission

process is in either Running or Suspended state.

R/W 0b

12:3 RESERVED RO -

2 Operate on Second Frame (OSF)

When set, this bit instructs the DMA Controller to process a second frame

of transmit data even before status for the first frame is obtained. This bit

affects the DMA Controller but not the MIL.

R/W 0b