Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

SMSC LAN9420/LAN9420i 37 Revision 1.22 (09-25-08)

DATASHEET

WRAL (Write All): If erase/write operations are enabled in the EEPROM, this command will cause the

contents of the E2P_DATA register to be written to every EEPROM memory location. The EPC_TO bit

is set if the EEPROM does not respond within 30ms.

Table 3.4, "Required EECLK Cycles", shown below, shows the number of EECLK cycles required for

each EEPROM operation.

3.3.5.3.2 HOST INITIATED MAC ADDRESS, SSID, SSVID RELOAD

The Host can initiate a reload of the MAC address, SSID, and SSVID from the EEPROM by issuing

the RELOAD command via the E2P command (E2P_CMD) register. If the first byte read from the

EEPROM is not A5h, it is assumed that the EEPROM is not present, or not programmed, and the

RELOAD operation will fail. The “EEPROM Loaded” bit indicates a successful reload of the MAC

address, SSID, and SSVID.

3.3.5.3.3 EEPROM COMMAND AND DATA REGISTERS

Refer to Section 4.2.11, "EEPROM Command Register (E2P_CMD)," on page 99 and Section 4.2.12,

"EEPROM Data Register (E2P_DATA)," on page 102 for a detailed description of these registers.

Supported EEPROM operations are described in these sections.

3.3.5.3.4 EEPROM TIMING

Refer to Section 5.8, "EEPROM Timing," on page 165 for detailed EEPROM timing specifications.

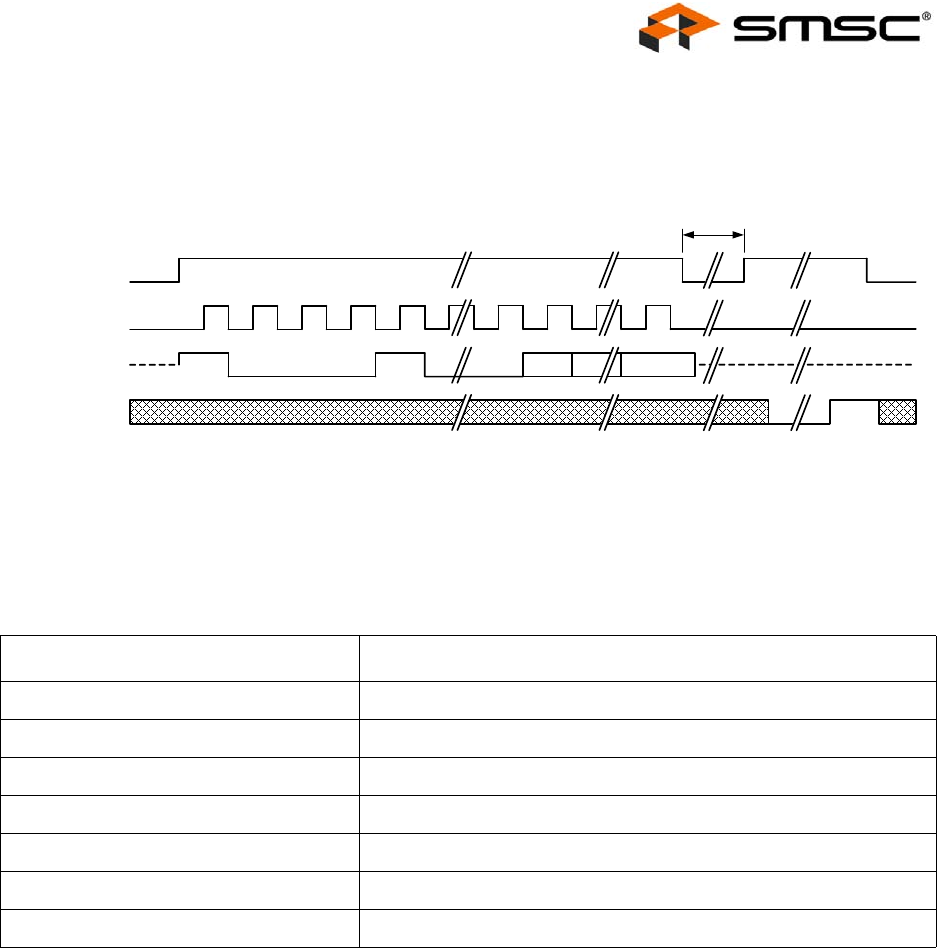

Figure 3.14 EEPROM WRAL Cycle

Table 3.4 Required EECLK Cycles

OPERATION REQUIRED EECLK CYCLES

ERASE 10

ERAL 10

EWDS 10

EWEN 10

READ 18

WRITE 18

WRAL 18

0

EECLK

EEDIO (INPUT)

EEDIO (OUTPUT)

EECS

1

D7 D0

0 01

t

CSL