Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

SMSC LAN9420/LAN9420i 45 Revision 1.22 (09-25-08)

DATASHEET

Receive Descriptor 3 (RDES3)

3.4.2.2 Transmit descriptors

The descriptors must be 4-DWORD (16-byte) aligned, while there are no alignment restrictions on

transmit buffer addresses. Providing two buffers, two byte-count buffers, and two address pointers in

each descriptor facilitates compatibility with various types of memory-management schemes.

Figure 3.17 shows the Transmit Descriptor format.

Table 3.8 RDES3 Bit Fields

BITS DESCRIPTION

31:0 Buffer 2 Address Pointer (Next Descriptor Address)

The RCH (Second Address Chained) bit (RDES1[24]) determines the usage of this field as

follows:

RCH is zero: This field contains the pointer to the address of buffer 2 in Host memory. The buffer

must be DWORD (32-bit) aligned (RDES3[1:0] = 00b). In the case where the buffer is not

DWORD aligned, the resulting behavior is undefined.

RCH is one: Descriptor chaining is in use and this field contains the pointer to the next descriptor

in Host memory. The descriptor must be 4-DWORD (16-byte) aligned (RDES3[3:0] = 0000b). In

the case where the buffer is not 4-DWORD aligned, the resulting behavior is undefined.

Note: If RER (RDES1[25]) is set, RCH is ignored and this field is treated as a pointer to buffer

2 as in the “RCH is zero” case above.

Host Actions: Initializes this field.

DMAC Actions: Reads this field upon opening a new DMA descriptor to obtain the buffer

address.

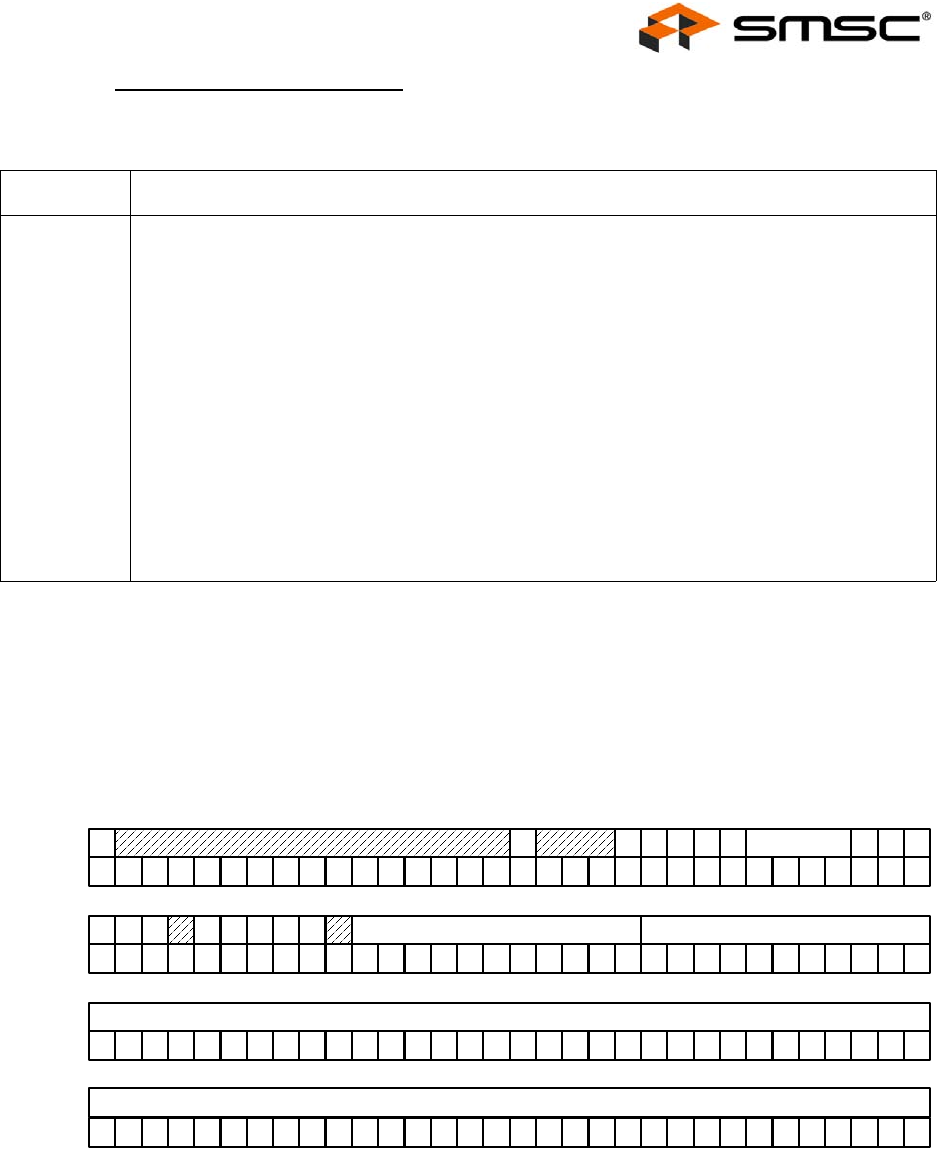

Figure 3.17 Transmit Descriptor

TDES1

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TDES2

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OW

TDES0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TDES3

BUFFER 1 ADDRESS POINTER

BUFFER 2 ADDRESS POINTER

RESERVED ES RES LC NC LT EC HF CC ED UE DE

IC LS FS R AC TE TC DP R TBS2 TBS1CK