Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

Revision 1.22 (09-25-08) 162 SMSC LAN9420/LAN9420i

DATASHEET

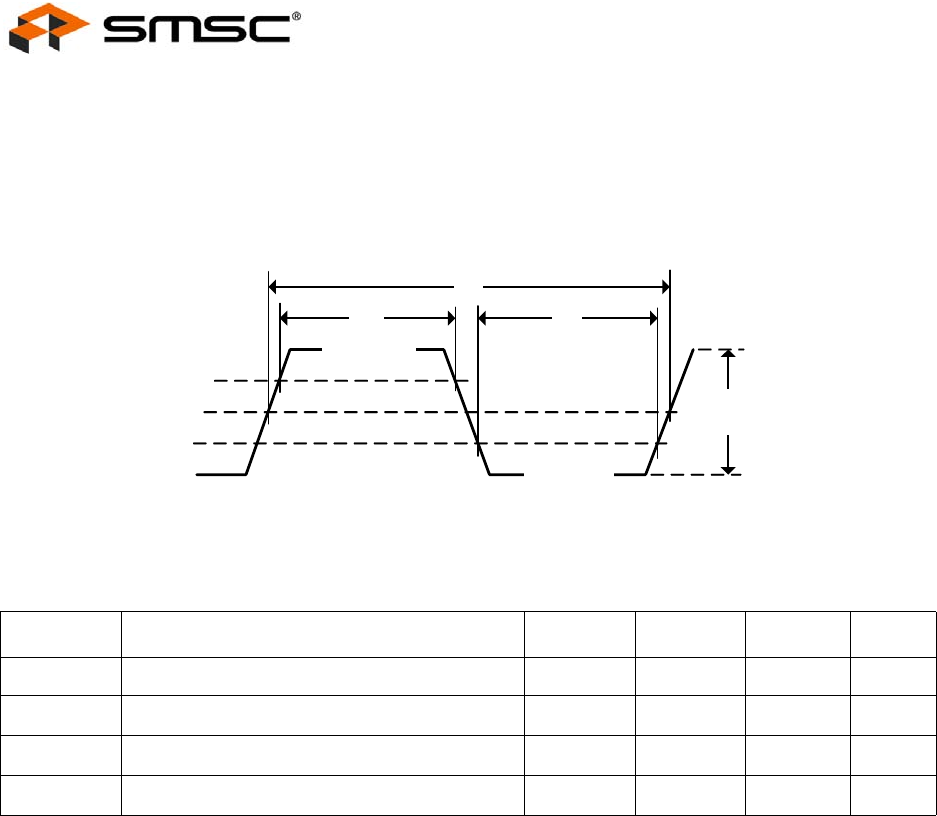

5.6 PCI Clock Timing

The following specifies the PCI clock requirements for LAN9420/LAN9420i:

Note 5.14 This slew rate must be met across the minimum peak-to-peak portion of the clock

waveform as shown in Figure 5.2.

Figure 5.2 PCI Clock Timing

Table 5.9 PCI Clock Timing Values

SYMBOL DESCRIPTION MIN TYP MAX UNITS

t

cyc

PCICLK cycle time 30 ∞ ns

t

high

PCICLK high time 11 ns

t

low

PCICLK low time 11 ns

-

PCICLK slew rate (Note 5.14)1 4V/ns

t

high

t

cyc

t

low

PCICLK

0.6*VDD33IO

0.2*VDD33IO

0.5*VDD33IO

0.4*VDD33IO

0.3*VDD33IO

0.4*VDD33IO p-to-p

(minimum)