www.ti.com

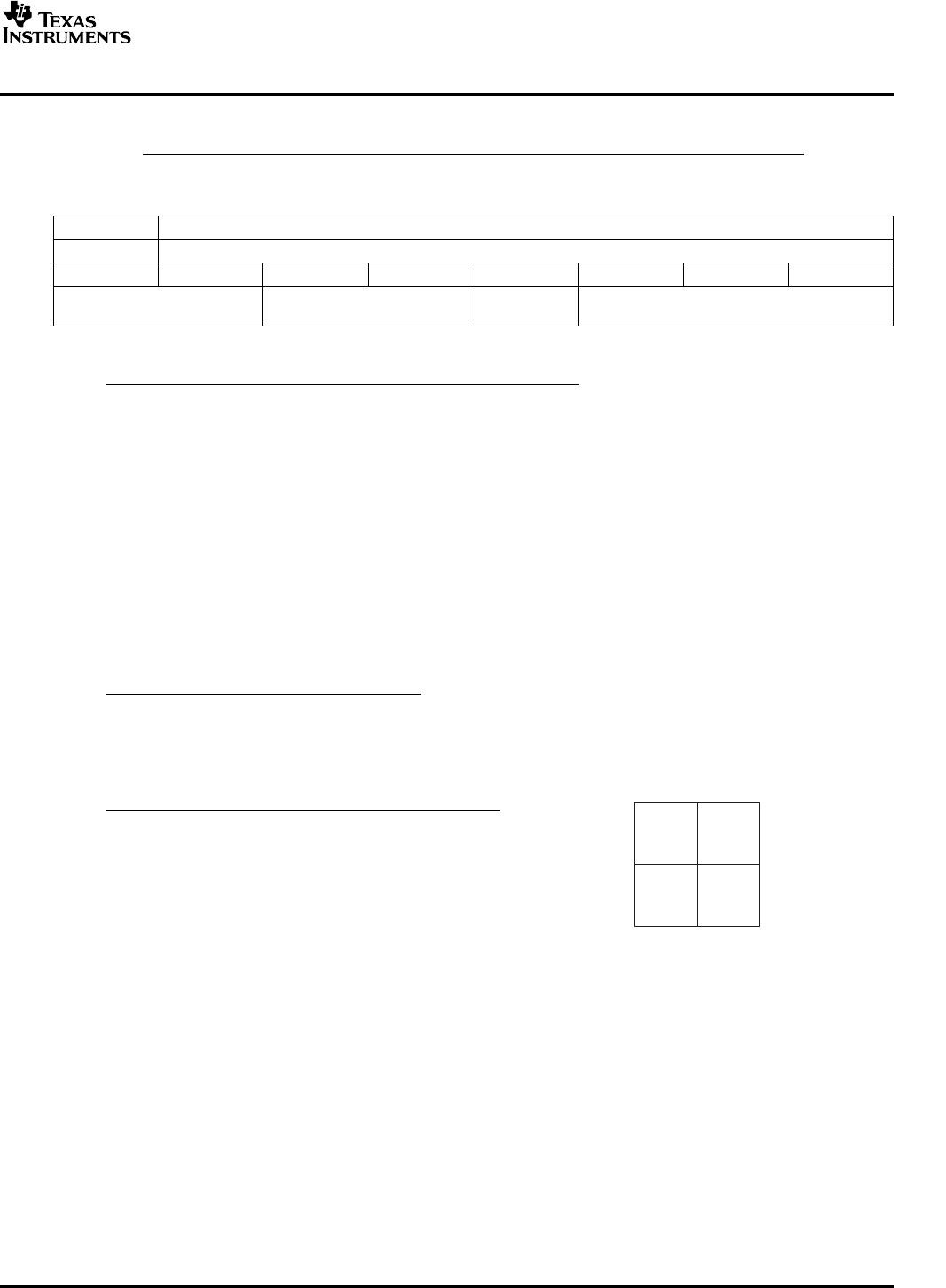

Quad 1 Quad 2

Quad 3 Quad 4

ProgrammingtheTMS320DM642

Note:TheunscaledDecoder2displaysinbothQuadrant2and3sinceDecoder2takespriority

overDecoder3whenbothareunscaled.

Table11.Decoder2Register

Address01h

Default12h

76543210

Capture

ReservedPositionCaptureSize

Enable

CaptureSizeBit2Bit1Bit0

Unscaled000

QSIF–176×120001

SIF–352×240(1/4NTSC)

010

(default)

QCIF–176×144011

CIF–352×288(1/4PAL)100

QVGA–320×240101

VGA–640×480110

Reserved111

CaptureEnableBit3

Disable(default)0

Enable1

PositionBit5Bit4

Quadrant100

Quadrant2(default)01

Quadrant310

Quadrant411

SLEU069A–February2006–RevisedJuly2006TVP5154EVMUser'sGuide29

SubmitDocumentationFeedback