2.7MDIOModule

2.7.1MDIOModuleComponents

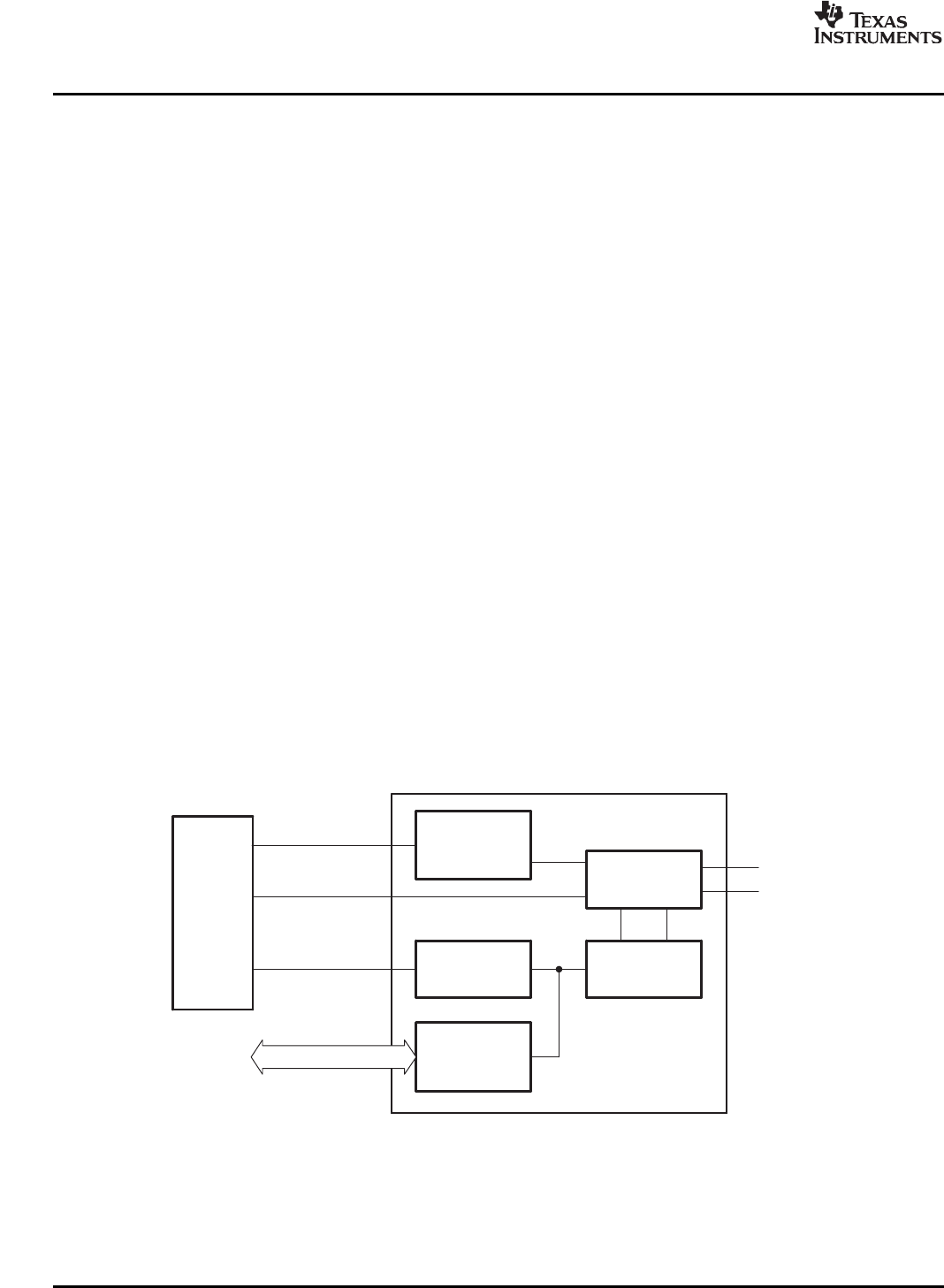

EMAC

control

module

Control

registers

and logic

PHY

monitoring

Peripheral

clock

MDIO

clock

generator

USERINT

MDIO

interface

polling

PHY

MDCLK

MDIO

LINKINT

Configuration bus

2.7.1.1MDIOClockGenerator

Architecture

Iftherateoftransmitpulseinterruptinputsismuchlessthanthetargettransmitpulseinterruptrate

specifiedinCMTXINTMAX,thentheinterruptsarenotblockedtotheCPU.Ifthetransmitpulseinterrupt

rateisgreaterthanthespecifiedtargetrateinCMTXINTMAX,theinterruptispacedattheratespecified

inthisregister,whichshouldbewrittenwithavaluebetween2and63inclusive,indicatingthetarget

numberofinterruptsper1msgoingtotheCPU.Similarly,thenumberofreceiveinterruptpulsestothe

CPUisalsoseparatelycontrolled.

TheMDIOmoduleisusedtomanageupto32physicallayer(PHY)devicesconnectedtotheEthernet

MediaAccessController(EMAC).TheDM646xdevicesupportsasinglePHYbeingconnectedtothe

EMACatanygiventime.TheMDIOmoduleisdesignedtoallowalmosttransparentoperationofthe

MDIOinterfacewithlittlemaintenancefromtheCPU.

TheMDIOmodulecontinuouslypolls32MDIOaddressesinordertoenumerateallPHYdevicesinthe

system.OnceaPHYdevicehasbeendetected,theMDIOmodulereadstheMDIOPHYlinkstatus

register(LINK)tomonitorthePHYlinkstate.LinkchangeeventsarestoredintheMDIOmodule,which

caninterrupttheCPU.ThisstoringoftheeventsallowstheCPUtopollthelinkstatusofthePHYdevice

withoutcontinuouslyperformingMDIOmoduleaccesses.However,whentheCPUmustaccesstheMDIO

moduleforconfigurationandnegotiation,theMDIOmoduleperformstheMDIOreadorwriteoperation

independentoftheCPU.Thisindependentoperationallowstheprocessortopollforcompletionor

interrupttheCPUoncetheoperationhascompleted.

TheMDIOmodule(Figure10)interfacestothePHYcomponentsthroughtwoMDIOpins(MDCLKand

MDIO),andtotheCPUthroughtheEMACcontrolmoduleandtheconfigurationbus.TheMDIOmodule

consistsofthefollowinglogicalcomponents:

•MDIOclockgenerator

•GlobalPHYdetectionandlinkstatemonitoring

•ActivePHYmonitoring

•PHYregisteruseraccess

Figure10.MDIOModuleBlockDiagram

TheMDIOclockgeneratorcontrolstheMDIOclockbasedonadivide-downoftheperipheralclock

(PLL1/6)intheEMACcontrolmodule.TheMDIOclockisspecifiedtorunupto2.5MHZ,althoughtypical

operationwouldbe1.0MHZ.Sincetheperipheralclockfrequencyisvariable(PLL1/6),theapplication

softwareordrivercontrolsthedivide-downamount.

EthernetMediaAccessController(EMAC)/ManagementDataInput/Output(MDIO) 34SPRUEQ6–December2007

SubmitDocumentationFeedback