2.16InterruptSupport

2.16.1EMACModuleInterruptEventsandRequests

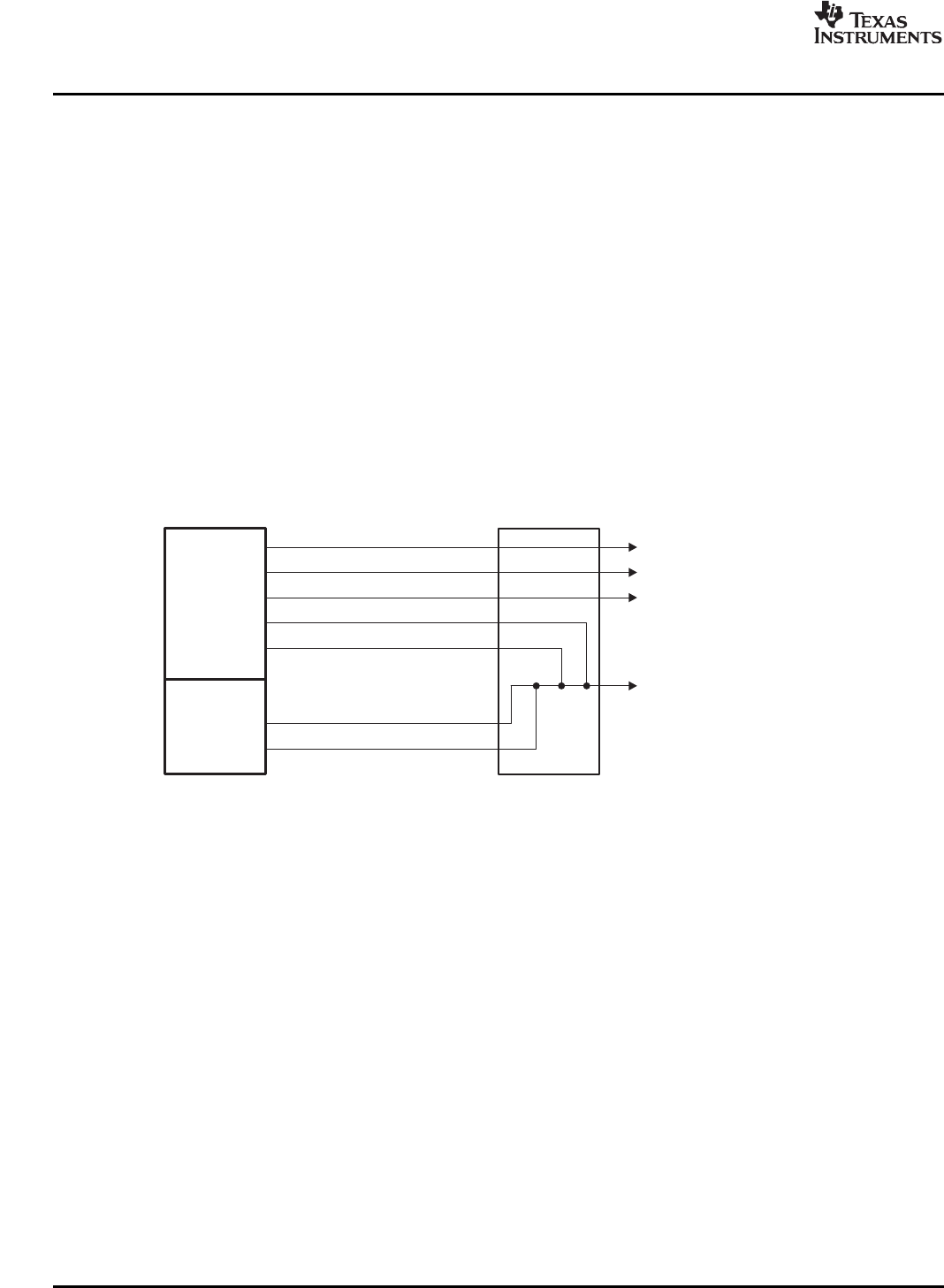

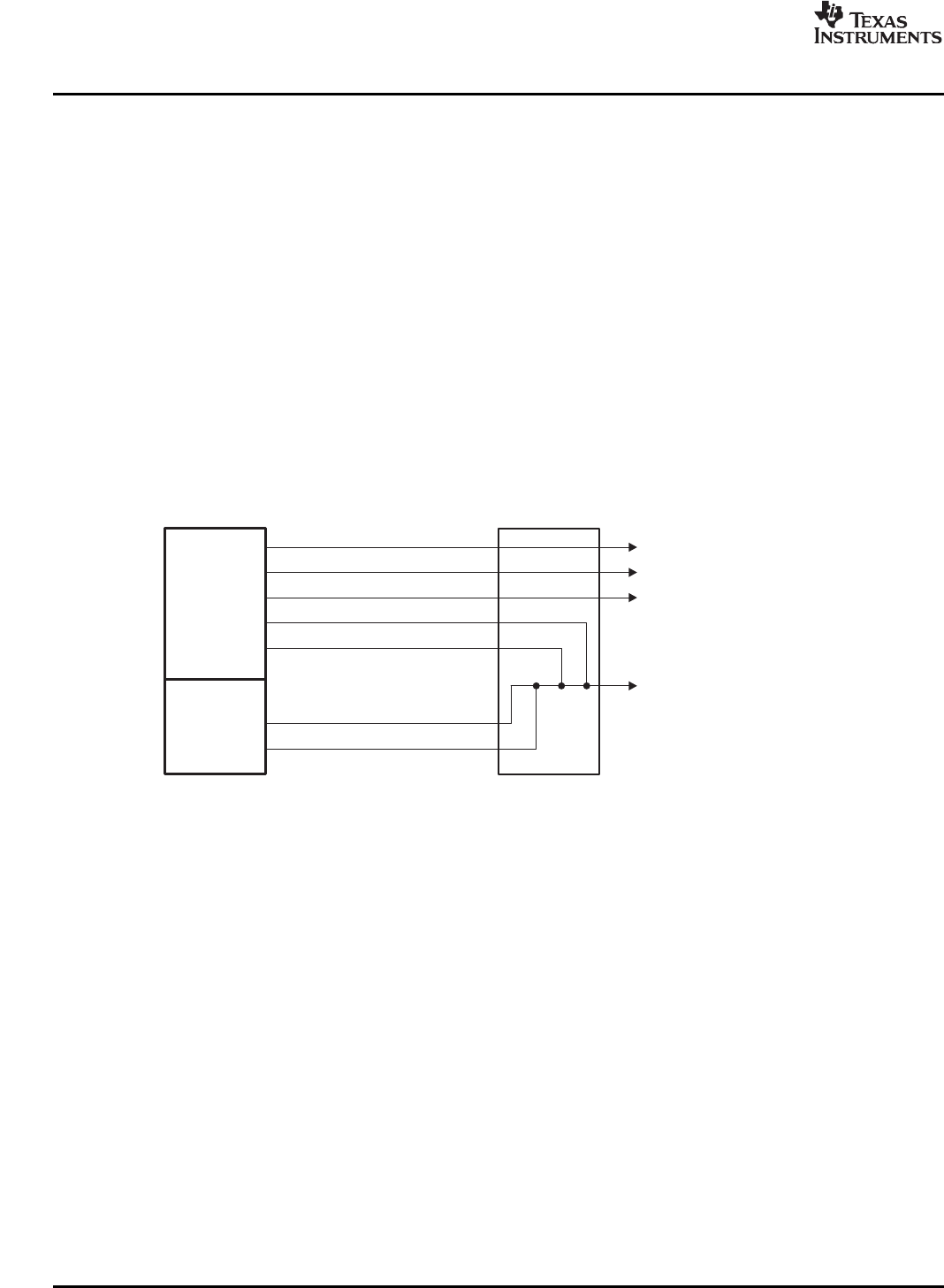

EMACcore

MDIOcore

RXTHRESHOLDPEND(0..7)

Receivethresholdinterrupt

RXPEND(0..7)

Receiveinterrupt

TXPEND(0..7)

Transmitinterrupt

STATPEND

HOSTPEND

MDIO_USER

Miscellaneousinterrupt

MDIO_LINKINT

Interruptcontrolandpacinglogic

2.16.1.1ReceiveThresholdInterrupts

Architecture

TheEMACmodulegeneratesthefollowinginterruptevents:

•RXTHRESHOLDPENDn:Receivethresholdinterruptforreceivechannels0through7

•RXPENDn:Receivepacketcompletioninterruptforreceivechannels0through7

•TXPENDn:Transmitpacketcompletioninterruptfortransmitchannels0through7

•STATPEND:Statisticsinterrupt

•HOSTPEND:Hosterrorinterrupt

•USERINT:MDIOuserInterrupt

•LINKINT:MDIOlinkInterrupt

AsshowninFigure12,theEMACandMDIOinterruptsaremultiplexedonfourinterruptslinesgoingto

theCPU.

Figure12.EMACControlModuleInterruptLogicDiagram

Eachoftheeightreceivechannelshaveacorrespondingreceivethresholdinterrupt

(RX_THRESH_PEND[0:7]).Thereceivethresholdinterruptsarelevelinterruptsthatremainasserted

untilthetriggeringconditionisclearedbythehost.Eachoftheeightthresholdinterruptsmaybe

individuallyenabledbysettingthecorrespondingbitinthereceiveinterruptmasksetregister

(RXINTMASKSET)to1.Eachoftheeightchannelinterruptsmaybeindividuallydisabledbyclearing

thecorrespondingbitinthereceiveinterruptmaskclearregister(RXINTMASKCLEAR)to0.Theraw

andmaskedreceiveinterruptstatusmaybereadfromthereceiveinterruptstatus(unmasked)register

(RXINTSTATRAW)andthereceiveinterruptstatus(masked)register(RXINTSTATMASKED),

respectively.AnRX_THRES_PEND[7:0]interruptbitisassertedwhenenabledandwhenthechannel’s

associatedreceivechannelnfreebuffercountregister(RXnFREEBUFFER)islessthanorequaltothe

channel’sassociatedreceivechannelnflowcontrolthresholdregister(RXnFLOWTHRESH).The

receivethresholdinterruptsusethesamefreebuffercountandthresholdlogicasdoesflowcontrol,but

theinterruptsareindependentlyenabledfromflowcontrol.Thethresholdinterruptsareintendedtogive

thehostanindicationthatresourcesarerunninglowforaparticularchannel(s).

EthernetMediaAccessController(EMAC)/ManagementDataInput/Output(MDIO) 56SPRUEQ6–December2007

SubmitDocumentationFeedback