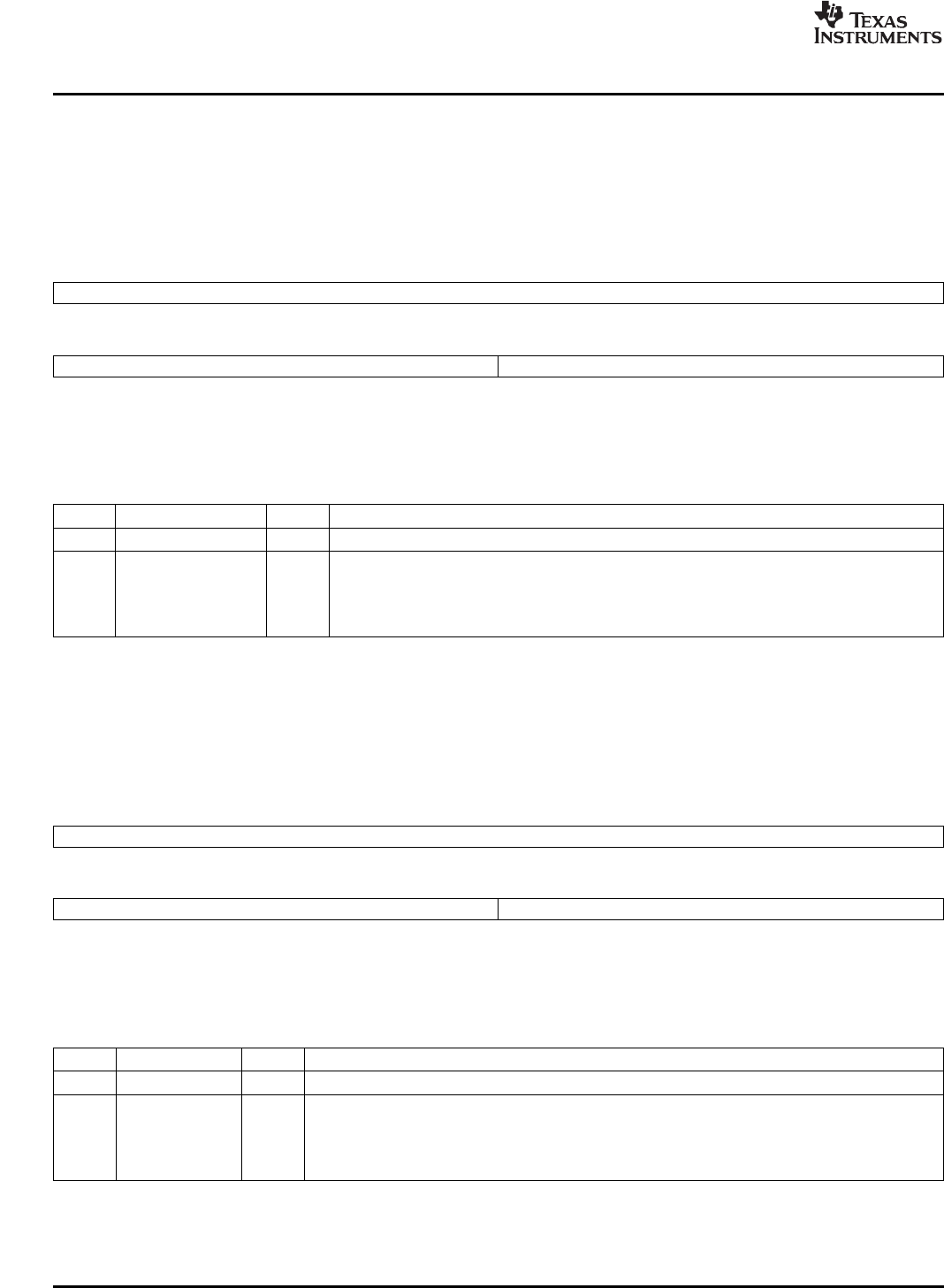

3.5EMACControlModuleReceiveThresholdInterruptEnableRegister

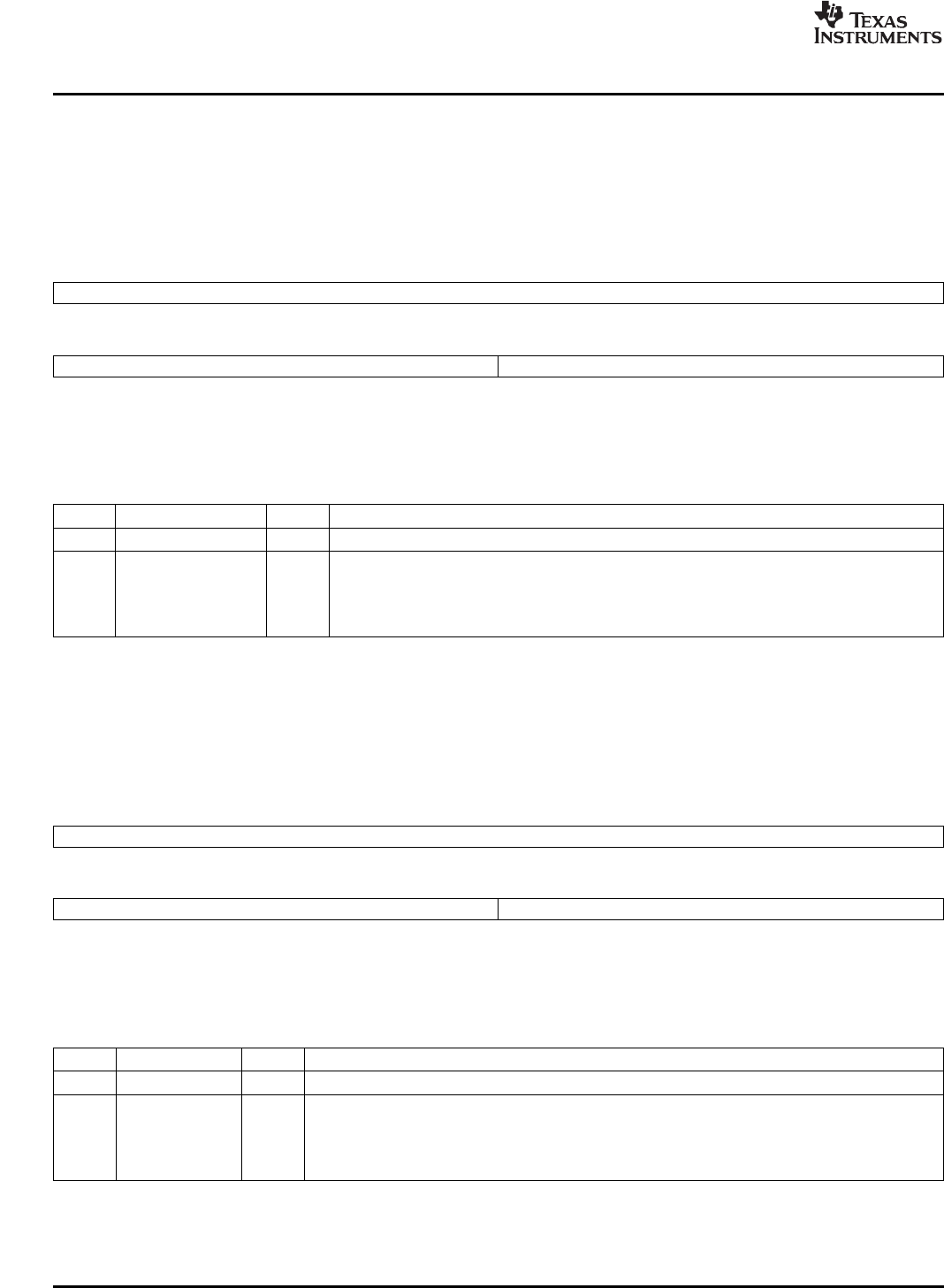

3.6EMACControlModuleReceiveInterruptEnableRegister(CMRXINTEN)

EMACControlModuleRegisters

(CMRXTHRESHINTEN)

Thereceivethresholdinterruptenableregister(CMRXTHRESHINTEN)isshowninFigure17and

describedinTable14.

Figure17.EMACControlModuleReceiveThresholdInterruptEnableRegister

(CMRXTHRESHINTEN)

3116

Reserved

R-0

15870

ReservedRXTHRESHEN

R-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table14.EMACControlModuleReceiveThresholdInterruptEnableRegister

(CMRXTHRESHINTEN)FieldDescriptions

BitFieldValueDescription

31-8Reserved0Reserved

7-0RXTHRESHEN[n]Receivethresholdinterrupt(RXTHRESHPENDn)enable.Eachbitcontrolsthecorresponding

channelnreceivethresholdinterrupt.

Bitn=0,channelnreceivethresholdinterrupt(RXTHRESHPENDn)isdisabled.

Bitn=1,channelnreceivethresholdinterrupt(RXTHRESHPENDn)isenabled.

Thereceiveinterruptenableregister(CMRXINTEN)isshowninFigure18anddescribedinTable15.

Figure18.EMACControlModuleReceiveInterruptEnableRegister(CMRXINTEN)

3116

Reserved

R-0

15870

ReservedRXPULSEEN

R-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table15.EMACControlModuleReceiveInterruptEnableRegister(CMRXINTEN)

FieldDescriptions

BitFieldValueDescription

31-8Reserved0Reserved

7-0RXPULSEEN[n]Receiveinterrupt(RXPENDn)enable.Eachbitcontrolsthecorrespondingchannelnreceive

interrupt.

Bitn=0,channelnreceiveinterrupt(RXPENDn)isdisabled.

Bitn=1,channelnreceiveinterrupt(RXPENDn)isenabled.

EthernetMediaAccessController(EMAC)/ManagementDataInput/Output(MDIO) 64SPRUEQ6–December2007

SubmitDocumentationFeedback