4.2MDIOControlRegister(CONTROL)

MDIORegisters

TheMDIOcontrolregister(CONTROL)isshowninFigure28anddescribedinTable26.

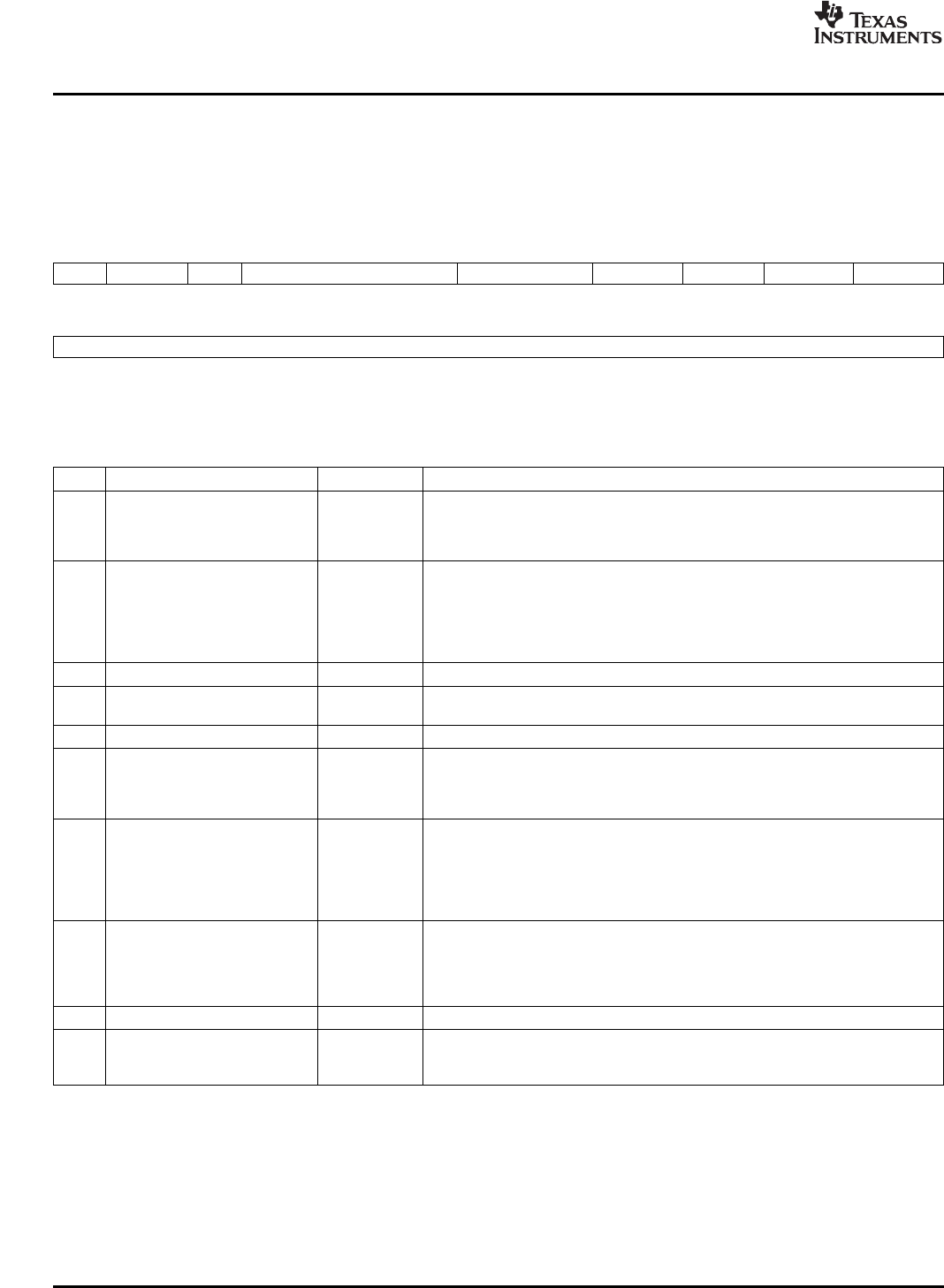

Figure28.MDIOControlRegister(CONTROL)

313029282423212019181716

IDLEENABLERsvdHIGHEST_USER_CHANNELReservedPREAMBLEFAULTFAULTENBReserved

R-1R/W-0R-0R-1R-0R/W-0R/W1C-0R/W-0R-0

150

CLKDIV

R/W-FFh

LEGEND:R/W=R=Readonly;R/W=Read/Write;W1C=Write1toclear,writeof0hasnoeffect;-n=valueafterreset

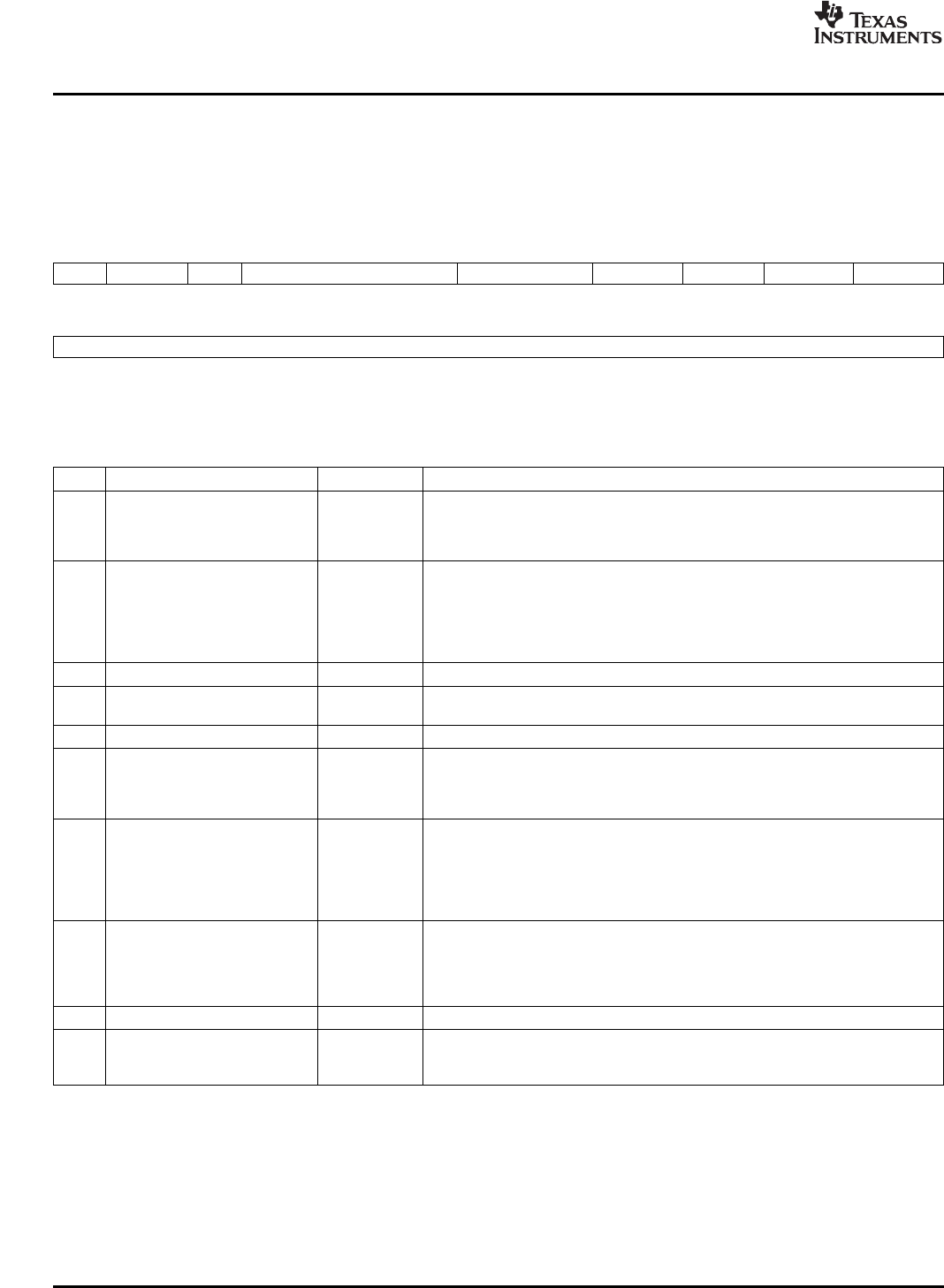

Table26.MDIOControlRegister(CONTROL)FieldDescriptions

BitFieldValueDescription

31IDLEStatemachineIDLEstatusbit

0Statemachineisnotinidlestate

1Statemachineisinidlestate

30ENABLEStatemachineenablecontrolbit.IftheMDIOstatemachineisactiveatthetime

itisdisabled,itwillcompletethecurrentoperationbeforehaltingandsettingthe

idlebit.

0DisablestheMDIOstatemachine

1EnabletheMDIOstatemachine

29Reserved0Reserved

28-24HIGHEST_USER_CHANNEL0-1FhHighestuserchannelthatisavailableinthemodule.Itiscurrentlysetto1.This

impliesthatMDIOUserAccess1isthehighestavailableuseraccesschannel.

23-21Reserved0Reserved

20PREAMBLEPreambledisable

0StandardMDIOpreambleisused

1DisablesthisdevicefromsendingMDIOframepreambles

19FAULTFaultindicator.Thisbitissetto1iftheMDIOpinsfailtoreadbackwhatthe

deviceisdrivingontothem.Thisindicatesaphysicallayerfaultandthemodule

statemachineisreset.Writinga1toitclearsthisbit,writinga0hasnoeffect.

0Nofailure

1Physicallayerfault;theMDIOstatemachineisreset

18FAULTENBFaultdetectenable.Thisbithastobesetto1toenablethephysicallayerfault

detection.

0Disablesthephysicallayerfaultdetection

1Enablesthephysicallayerfaultdetection

17-16Reserved0Reserved

15-0CLKDIV0-FFFFhClockDividerbits.Thisfieldspecifiesthedivisionratiobetweentheperipheral

clockandthefrequencyofMDCLK.MDCLKisdisabledwhenCLKDIVissetto

0.MDCLKfrequency=peripheralclockfrequency/(CLKDIV+1).

72EthernetMediaAccessController(EMAC)/ManagementDataInput/Output(MDIO)SPRUEQ6–December2007

SubmitDocumentationFeedback