5.11MACInputVectorRegister(MACINVECTOR)

5.12MACEndOfInterruptVectorRegister(MACEOIVECTOR)

EthernetMediaAccessController(EMAC)Registers

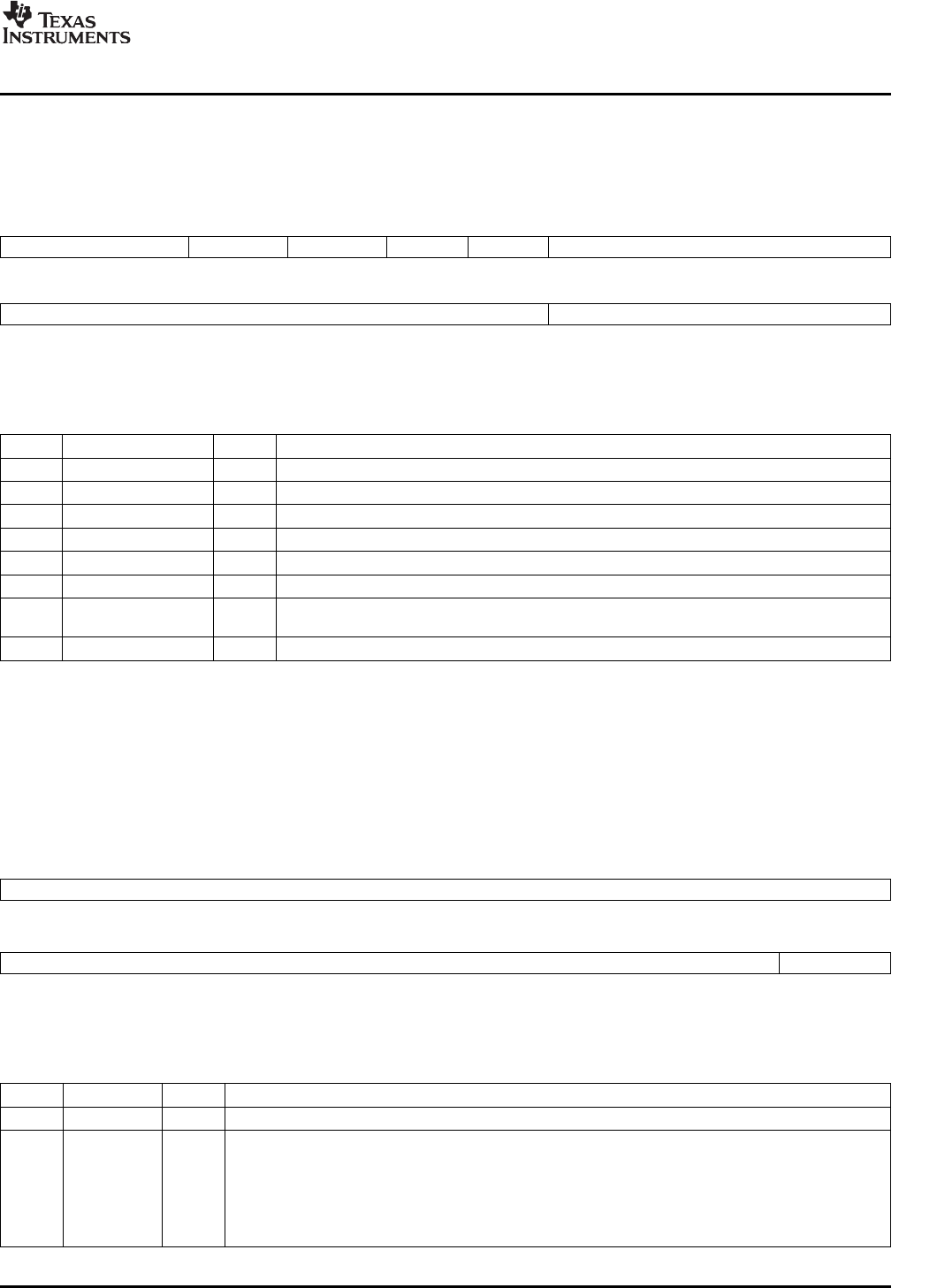

TheMACinputvectorregister(MACINVECTOR)isshowninFigure51anddescribedinTable50.

Figure51.MACInputVectorRegister(MACINVECTOR)

3128272625242316

ReservedSTATPENDHOSTPENDLINKINTUSERINTTXPEND

R-0R-0R-0R-0R-0R-0

15870

RXTHRESHPENDRXPEND

R-0R-0

LEGEND:R=Readonly;-n=valueafterreset

Table50.MACInputVectorRegister(MACINVECTOR)FieldDescriptions

BitFieldValueDescription

31-28Reserved0Reserved

27STATPEND0-1EMACmodulestatisticsinterrupt(STATPEND)pendingstatusbit.

26HOSTPEND0-1EMACmodulehosterrorinterrupt(HOSTPEND)pendingstatusbit.

25LINKINT0-1MDIOmodulelinkchangeinterrupt(LINKINT)pendingstatusbit.

24USERINT0-1MDIOmoduleuserinterrupt(USERINT)pendingstatusbit.

23-16TXPEND0-FFhTransmitchannels0-7interruptpending(TXPENDn)statusbit.Bit16istransmitchannel0.

15-8RXTHRESHPEND0-FFhReceivethresholdchannels0-7interruptpending(RXTHRESHPENDn)statusbit.Bit8is

receivechannel0.

7-0RXPEND0-FFhReceivechannels0-7interruptpending(RXPENDn)statusbit.Bit0isreceivechannel0.

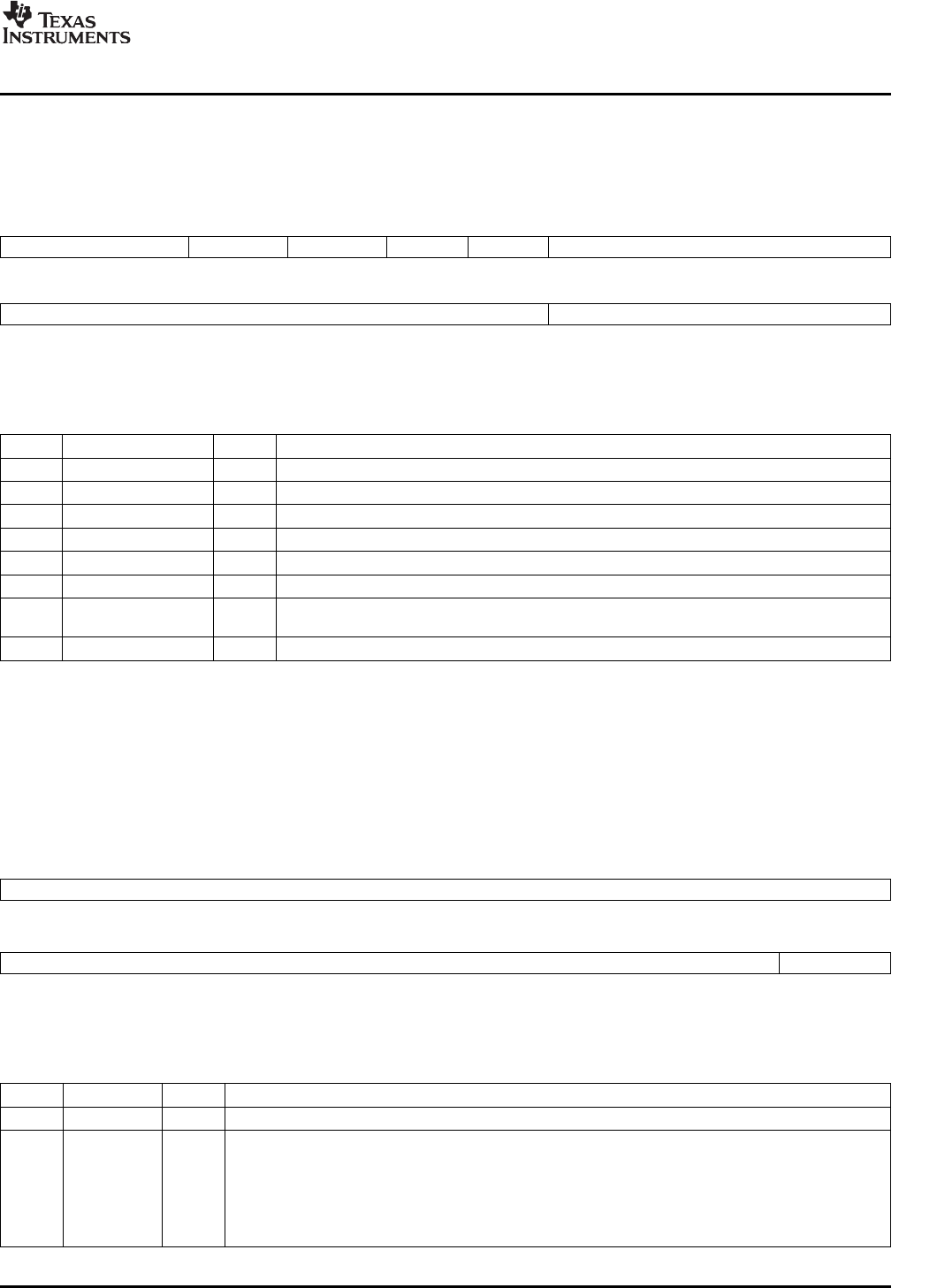

TheMACendofinterruptvectorregister(MACEOIVECTOR)isshowninFigure52anddescribedin

Table51.

Figure52.MACEndOfInterruptVectorRegister(MACEOIVECTOR)

3116

Reserved

R-0

15210

ReservedEOI

R-0R/W-0

LEGEND:R=Readonly;R/W=Read/Write;-n=valueafterreset

Table51.MACEndOfInterruptVectorRegister(MACEOIVECTOR)FieldDescriptions

BitFieldValueDescription

31-2Reserved0Reserved

1-0EOI0-3hEndofinterrupt.

0EndofinterruptprocessingforRXTHRESHinterrupt.

1hEndofinterruptprocessingforRXPULSEinterrupt.

2hEndofinterruptprocessingforTXPULSEinterrupt.

3hEndofinterruptprocessingforMiscellaneousinterrupt.

SPRUEQ6–December2007EthernetMediaAccessController(EMAC)/ManagementDataInput/Output(MDIO)95

SubmitDocumentationFeedback