Functional Description

MITX-430/MITX-440-DVI-2E Installation and Use Guide (6806800K37B)

64

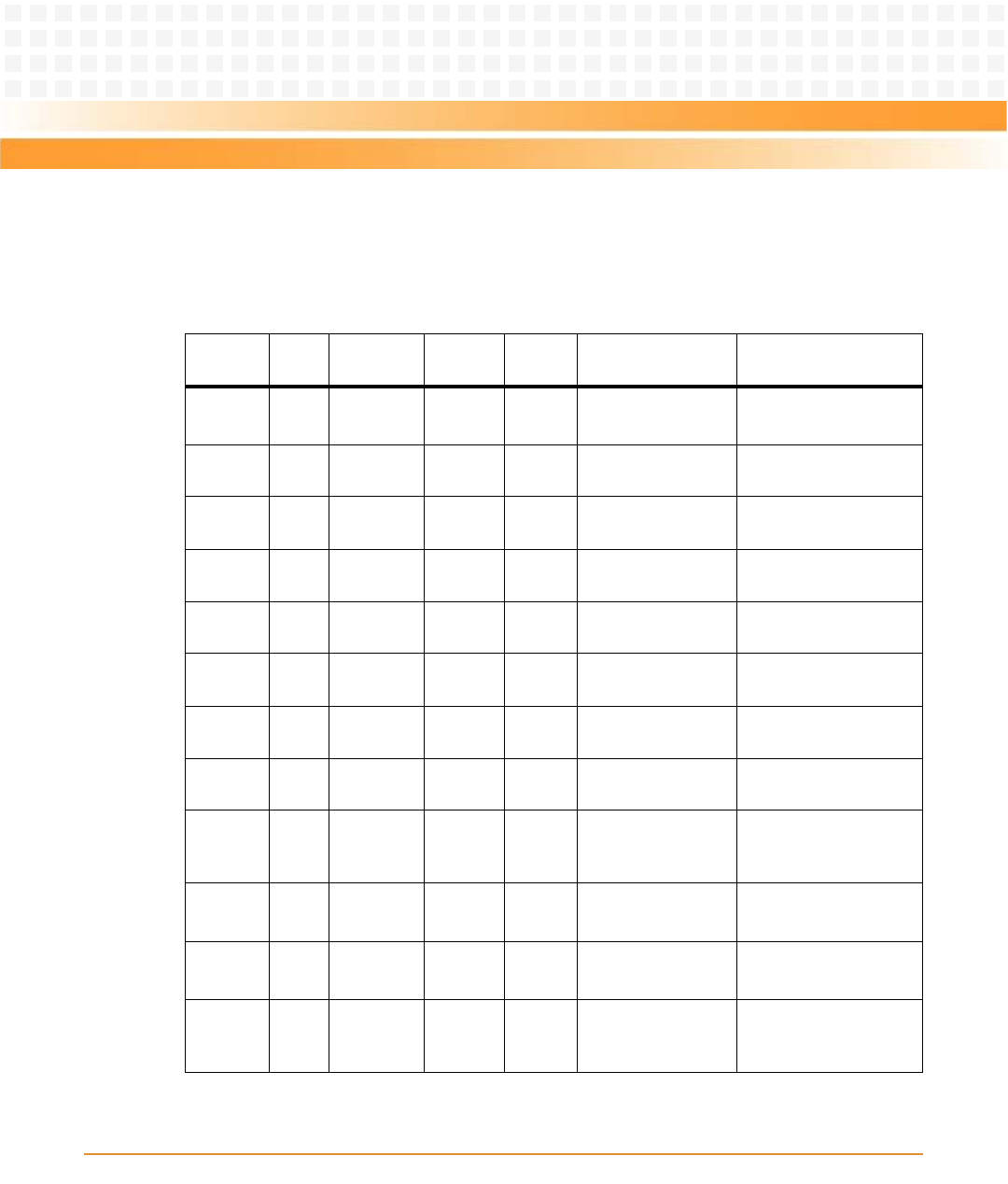

4.12.2 ICH8-M GPIO

Table 4-3 describes the ICH8-M GPIO definition.

Table 4-3 ICH8-M GPIO Definition

Name Type Tolerance

Power

Well Default Signal Description Implementation

GPIO0 I/O 3.3V Core GPI Multiplexed with

BM_BUSY#

Unused, PU VCC3V3

GPIO1 I/O 3.3V Core GPI Multiplexed with

TACH1

Used as IDE 80 pin

cable detect

GPIO2 I/OD 5V Core GPI Multiplexed with

PIRQ[H:E]#

Unused, PU VCC3V3

GPIO3 I/OD 5V Core GPI Multiplexed with

PIRQ[H:E]#

Unused, PU VCC3V3

GPIO4 I/OD 5V Core GPI Multiplexed with

PIRQ[H:E]#

Unused, PU VCC3V3

GPIO5 I/OD 5V Core GPI Multiplexed with

PIRQ[H:E]#

Unused, PU VCC3V3

GPIO6 I/O 3.3V Core GPI Unmultiplexed Used for board ID, PU

VCC3V3

GPIO7 I/O 3.3V Core GPI Unmultiplexed Used for board ID, PU

VCC3V3

GPIO8 I/O 3.3V Resume GPI Unmultiplexed Used as BIOS write

protect (WP) signal, PU

VCC3V3DUAL

GPIO9 I/O 3.3V Resume GPI Multiplexed with

WOL_EN

Unused, PU

VCC3V3DUAL

GPIO10 I/O 3.3V Resume GPI Multiplexed with

SusPwrAck/ALERT#

Unused, PU

VCC3V3DUAL

GPIO11 I/O 3.3V Resume Native Multiplexed with

SMBALERT#

Used for SMBus alert

signal, PU

VCC3V3DUAL