28 Intel® 41110 Serial to Parallel PCI Bridge Design Guide

Board Layout Guidelines

Note: Each interface will set the trace spacing based on its signal integrity of differential impedance

requirements. For the purposes of the building the transmission line models, it is assumed the

artwork is very accurate and therefore a constant. All the variability in the trace spacing is the result

of the tolerances of the trace width.

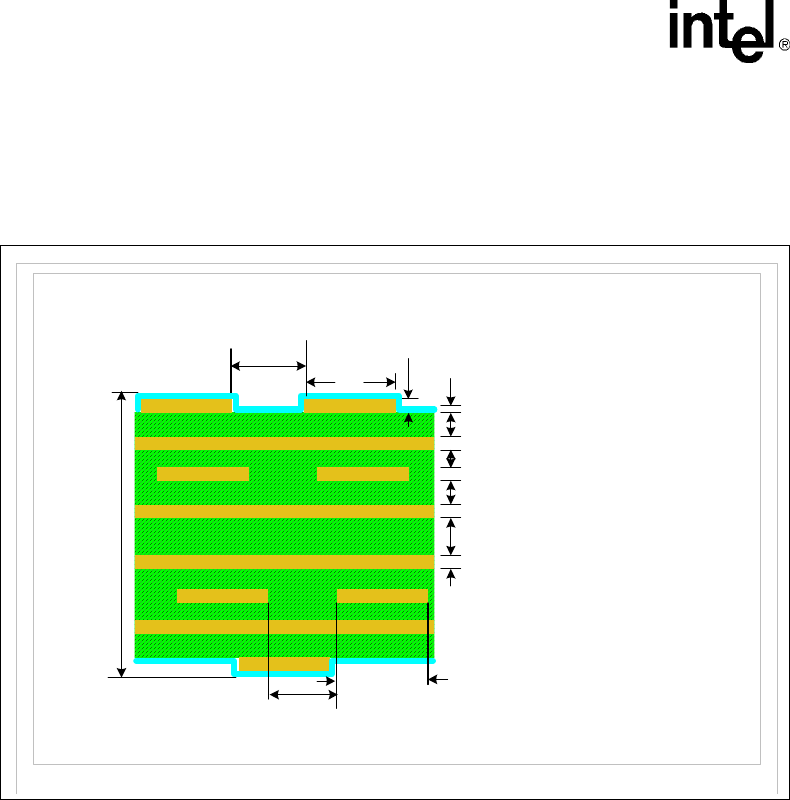

Figure 14. Adapter Card Stackup

B1436-01

L1

L2 (GND)

L8

L7 (GND)

Trace

Width

Total Thickenss

Trace Height 1

Plane Thickness

Solder Mask Thickness

L1

L4

L4 (VCC)

L5 (VCC)

Trace Height 3

L3

Trace Height 2

L3

L4

Microstrip

Microstrip

Stripline

Trace

Width

Trace

Spacing

Stripline

Core Thickness

Microstrip Trace Thickness

Stripline Trace Thickness

Trace

Spacing