Intel® 41110 Serial to Parallel PCI Bridge Design Guide 57

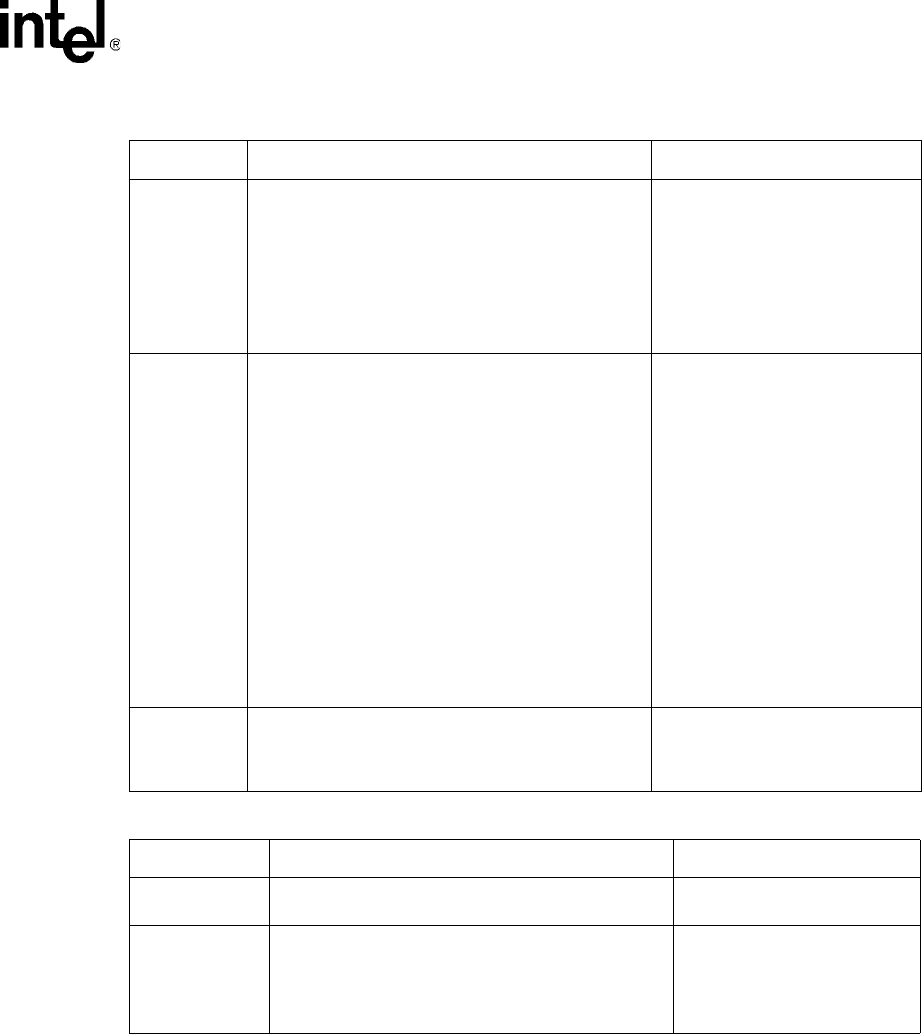

Design Guide Checklist

A_M66EN

Controls frequency of the PCI segment when running

in conventional PCI mode (33 MHz or 66 MHz):

0 = 33 MHz PCI

1 = 66 MHz PCI

• Pull-up using a 8.2KΩ resistor when the PCI bus is

to operate at 66 MHz and not already pulled up by

system board. This signal is grounded for 33 MHz

operation.

Sampled on the rising edge of

PERST#.

A_PCIXCAP

Connects directly to the PCIXCAP pin on the PCI slot.

Connect to VCC33 through an 8.2KΩ pullup resistor.

• Design without secondary PCI/PCI-

X Slot

— If there is at least one legacy

PCI device on the PCI/PCI-X

bus, tie this pin directly to

GND.

— If all devices are PCI-X

capable and there is at least

one PCI-X device that only

supports maximum PCI-X

66MHz on the secondary PCI

bus, pull down to GND

through 10K

Ω series resistor

parallel with a 0.01uF

capacitor.

— If all secondary PCI-X

devices (and the bus loading)

support PCI-X 133MHz,

connect PCIXCAP to 3.3V

through an 8.2K

Ω resistor

IDSEL

The series resistor on IDSEL should be 200Ω ±5% if it

is exclusively PCIX mode. If it is PCI mode or mixed

PCI/ PCIX mode is intended, 510 ohms is

recommended.

Table 21. Miscellaneous Signals

Signals Recommendations Reason/Impact

RSTIN#

Used for debug purposes. Connect to VCC33 through

an 8.2KΩ pullup resistor for normal operation.

A_STRAP0,

A_STRAP1,

A_STRAP2,

A_STRAP6,

RESERVED [8:1]

These signals REQUIRE external pull-downs to GND

on the board 8.2KΩ unless otherwise stated.

Table 20. PCI/PCI-X Interface Signals (Sheet 2 of 2)

Signals Recommendations Reason/Impact