30 Intel® 41110 Serial to Parallel PCI Bridge Design Guide

PCI-X Layout Guidelines

Note: PCI Express Assert_INTx/Deassert_INTx messages are not inhibited by the BME bit.

8.1.1 Interrupt Routing for Devices Behind a Bridge

Given the legacy interrupt sharing scheme shown in Table 5, to get the best legacy interrupt

performance (by reducing interrupt sharing), adapter boards have to select the appropriate

A_INTX# (where X is A, B, C or D) input pin to use on the PCI bus segment. The chosen interrupt

input also imposes a PCI device number requirement for the interrupt source as specified in the

PCI-to-PCI Bridge specification and reproduced in Table 5

.

8.2 PCI Arbitration

The 41110 supports a high-performance internal PCI arbiter that supports up to seven masters on

each PCI segment A and B PCI Buses. The request inputs into the internal arbiter include: six

external request inputs and 1 internal request input. All request inputs to the internal arbiter are

split into two groups, a high priority group and a low priority group. Any master, including the

internal master, can be programmed to be in either of the two groups. This could also mean that all

the request inputs into the arbiter could be in one single group. Within a group, priority is round-

robin. The entire low-priority group represents one slot in the high priority group. The 41110

provides a 16-bit arbiter control register to control two aspects of the internal arbiter behavior:

• Priority group for a master (i.e., whether a master is in low priority group or high priority

group).

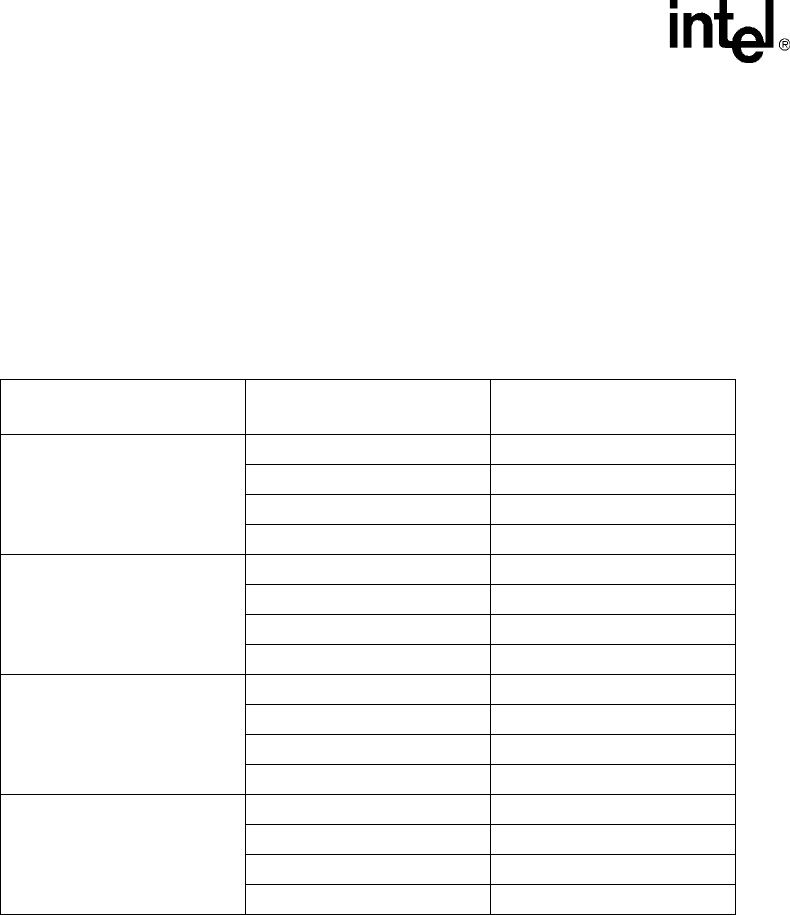

Table 5. Interrupt Binding for Devices Behind a Bridge

Device Number on

Secondary Bus

Interrupt Pin on Device Interrupt on 41110 Bridge

-

a

. 4, 8

b

, 12, 16, 20, 24, 28

INTA# INTA#

INTB# INTB#

INTC# INTC#

INTD# INTD#

1, 5, 9

b

, 13, 17, 21, 25, 29

INTA# INTB#

INTB# INTC#

INTC# INTD#

INTD# INTA#

2, 6, 10

b

, 14, 18, 22, 26, 30

INTA# INTC#

INTB# INTD#

INTC# INTA#

INTD# INTB#

3, 7, 11

b

, 15, 19, 23, 27, 31

INTA# INTD#

INTB# INTA#

INTC# INTB#

INTD# INTC#

a. Device number 0 is reserved for the Bridge and should not be assigned to secondary devices.

b. AD[27:24] which correspond to devices 11:8 should not be used for IDSEL# connections as these signals are used

when accessing the extended configuration space in the bridge from the secondary bus.