Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families 23

Datasheet Volume One

Overview

1.7 Related Documents

Refer to the following documents for additional information.

TDP Thermal Design Power

TSOD Thermal Sensor on DIMM

UDIMM Unbuffered Dual In-line Module

Uncore The portion of the processor comprising the shared cache, IMC, HA, PCU, UBox,

and Intel QPI link interface.

Unit Interval Signaling convention that is binary and unidirectional. In this binary signaling,

one bit is sent for every edge of the forwarded clock, whether it be a rising edge

or a falling edge. If a number of edges are collected at instances t

1

, t

2

, t

n

,...., t

k

then the UI at instance “n” is defined as:

UI

n

= t

n

- t

n

- 1

V

CC

Processor core power supply

V

SS

Processor ground

V

CCD_01,

V

CCD_23

Variable power supply for the processor system memory interface. VCCD is the

generic term for V

CCD_01,

V

CCD_23.

x1 Refers to a Link or Port with one Physical Lane

x4 Refers to a Link or Port with four Physical Lanes

x8 Refers to a Link or Port with eight Physical Lanes

x16 Refers to a Link or Port with sixteen Physical Lanes

Term Description

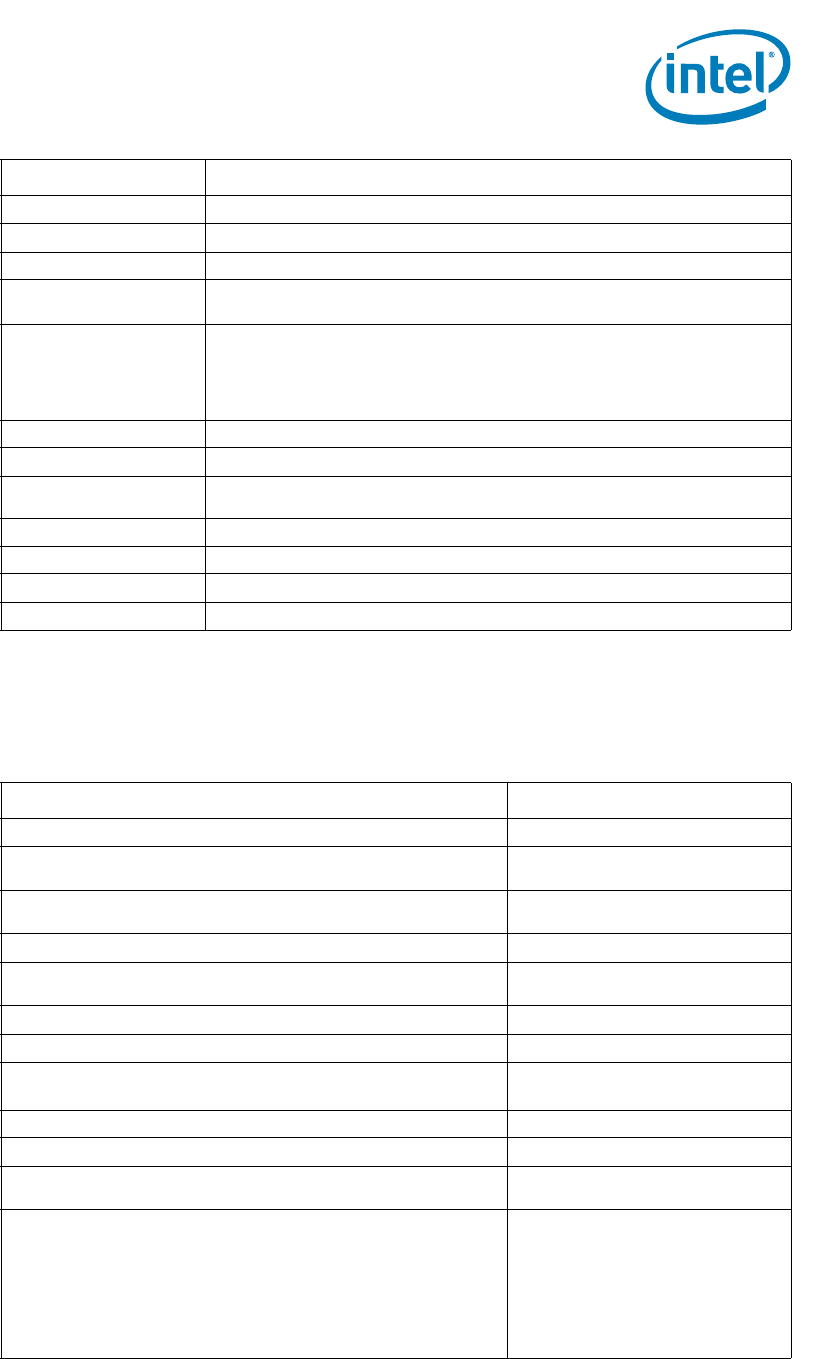

Table 1-1. Referenced Documents (Sheet 1 of 2)

Document Location

Intel® Xeon® Processor E5 Product Family Datasheet Volume Two http://www.intel.com

Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families

Thermal/Mechanical Design Guide

http://www.intel.com

Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families

– BSDL (Boundary Scan Description Language)

http://www.intel.com

Intel® C600 Series Chipset Data Sheet http://www.intel.com

Intel® 64 and IA-32 Architectures Software Developer’s Manual

(SDM) Volumes 1, 2, and 3

http://www.intel.com

Advanced Configuration and Power Interface Specification 3.0 http://www.acpi.info

PCI Local Bus Specification 3.0 http://www.pcisig.com/specifications

PCI Express Base Specification - Revision 2.1 and 1.1

PCI Express Base Specification - Revision 3.0

http://www.pcisig.com

System Management Bus (SMBus) Specification http://smbus.org/

DDR3 SDRAM Specification http://www.jedec.org

Low (JESD22-A119) and High (JESD-A103) Temperature Storage Life

Specifications

http://www.jedec.org

Intel 64 and IA-32 Architectures Software Developer's Manuals

• Volume 1: Basic Architecture

• Volume 2A: Instruction Set Reference, A-M

• Volume 2B: Instruction Set Reference, N-Z

• Volume 3A: System Programming Guide

• Volume 3B: System Programming Guide

Intel® 64 and IA-32 Architectures Optimization Reference Manual

http://www.intel.com/products/proce

ssor/manuals/index.htm