Power Management

92 Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families

Datasheet Volume One

For legacy operating systems, P_LVLx I/O reads are converted within the processor to

the equivalent MWAIT C-state request. Therefore, P_LVLx reads do not directly result in

I/O reads to the system. The feature, known as I/O MWAIT redirection, must be

enabled in the BIOS. To enable it, refer to the

Intel® 64 and IA-32 Architectures

Software Developer’s Manual (SDM) Volumes 1, 2, and 3.

Note: The P_LVLx I/O Monitor address needs to be set up before using the P_LVLx I/O read

interface. Each P-LVLx is mapped to the supported MWAIT(Cx) instruction as follows.

The BIOS can write to the C-state range field of the PMG_IO_CAPTURE MSR to restrict

the range of I/O addresses that are trapped and emulate MWAIT like functionality. Any

P_LVLx reads outside of this range does not cause an I/O redirection to MWAIT(Cx) like

request. They fall through like a normal I/O instruction.

Note: When P_LVLx I/O instructions are used, MWAIT substates cannot be defined. The

MWAIT substate is always zero if I/O MWAIT redirection is used. By default, P_LVLx I/O

redirections enable the MWAIT 'break on EFLAGS.IF’ feature which triggers a wakeup

on an interrupt even if interrupts are masked by EFLAGS.IF.

4.2.4 Core C-states

The following are general rules for all core C-states, unless specified otherwise:

• A core C-State is determined by the lowest numerical thread state (for example,

Thread 0 requests C1E while Thread 1 requests C3, resulting in a core C1E state).

See Table 4-7.

• A core transitions to C0 state when:

— an interrupt occurs.

— there is an access to the monitored address if the state was entered via an

MWAIT instruction.

• For core C1/C1E, and core C3, an interrupt directed toward a single thread wakes

only that thread. However, since both threads are no longer at the same core

C-state, the core resolves to C0.

• An interrupt only wakes the target thread for both C3 and C6 states. Any interrupt

coming into the processor package may wake any core.

4.2.4.1 Core C0 State

The normal operating state of a core where code is being executed.

4.2.4.2 Core C1/C1E State

C1/C1E is a low power state entered when all threads within a core execute a HLT or

MWAIT(C1/C1E) instruction.

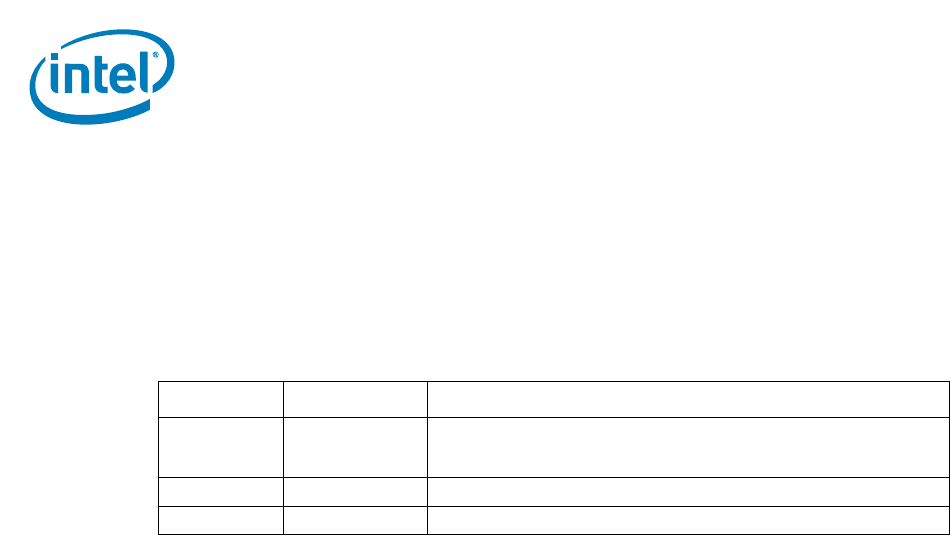

Table 4-8. P_LVLx to MWAIT Conversion

P_LVLx MWAIT(Cx) Notes

P_LVL2 MWAIT(C3) The P_LVL2 base address is defined in the PMG_IO_CAPTURE MSR,

described in the

Intel® 64 and IA-32 Architectures Software

Developer’s Manual (SDM) Volumes 1, 2, and 3.

P_LVL3 MWAIT(C6) C6. No sub-states allowed.

P_LVL4 MWAIT(C7) C7. No sub-states allowed.