Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families 65

Datasheet Volume One

2.5.2.8.2 Supported Responses

The typical client response is a passing FCS, a passing Completion Code and valid data.

Under some conditions, the client’s response will indicate a failure.

The PECI client response can also vary depending on the address and data. It will

respond with a passing completion code if it successfully submits the request to the

appropriate location and gets a response.

2.5.2.9 RdPCIConfigLocal()

The RdPCIConfigLocal() command provides sideband read access to the PCI

configuration space that resides within the processor. This includes all processor IIO

and uncore registers within the PCI configuration space as described in the Intel®

Xeon® Processor E5 Product Family Datasheet Volume Two document.

PECI originators may conduct a device/function enumeration sweep of this space by

issuing reads in the same manner that the BIOS would. A response of all 1’s may

indicate that the device/function/register is unimplemented even with a ‘passing’

completion code. Alternatively, reads to unimplemented or hidden registers may return

a completion code of 0x90 indicating an invalid request. It is also possible that reads to

function 0 of non-existent IIO devices issued prior to BIOS POST may return all ‘0’s

with a passing completion code. PECI originators can access this space even prior to

BIOS enumeration of the system buses. There is no read restriction on accesses to

locked registers.

PCI configuration addresses are constructed as shown in Figure 2-46. Under normal in-

band procedures, the Bus number would be used to direct a read or write to the proper

device. PECI reads to the processor IIO devices should specify a bus number of ‘0000’

and reads to the rest of the processor uncore should specify a bus number of ‘0001’ for

bits [23:20] in Figure 2-46. Any request made with a bad Bus number is ignored and

the client will respond with all ‘0’s and a ‘passing’ completion code.

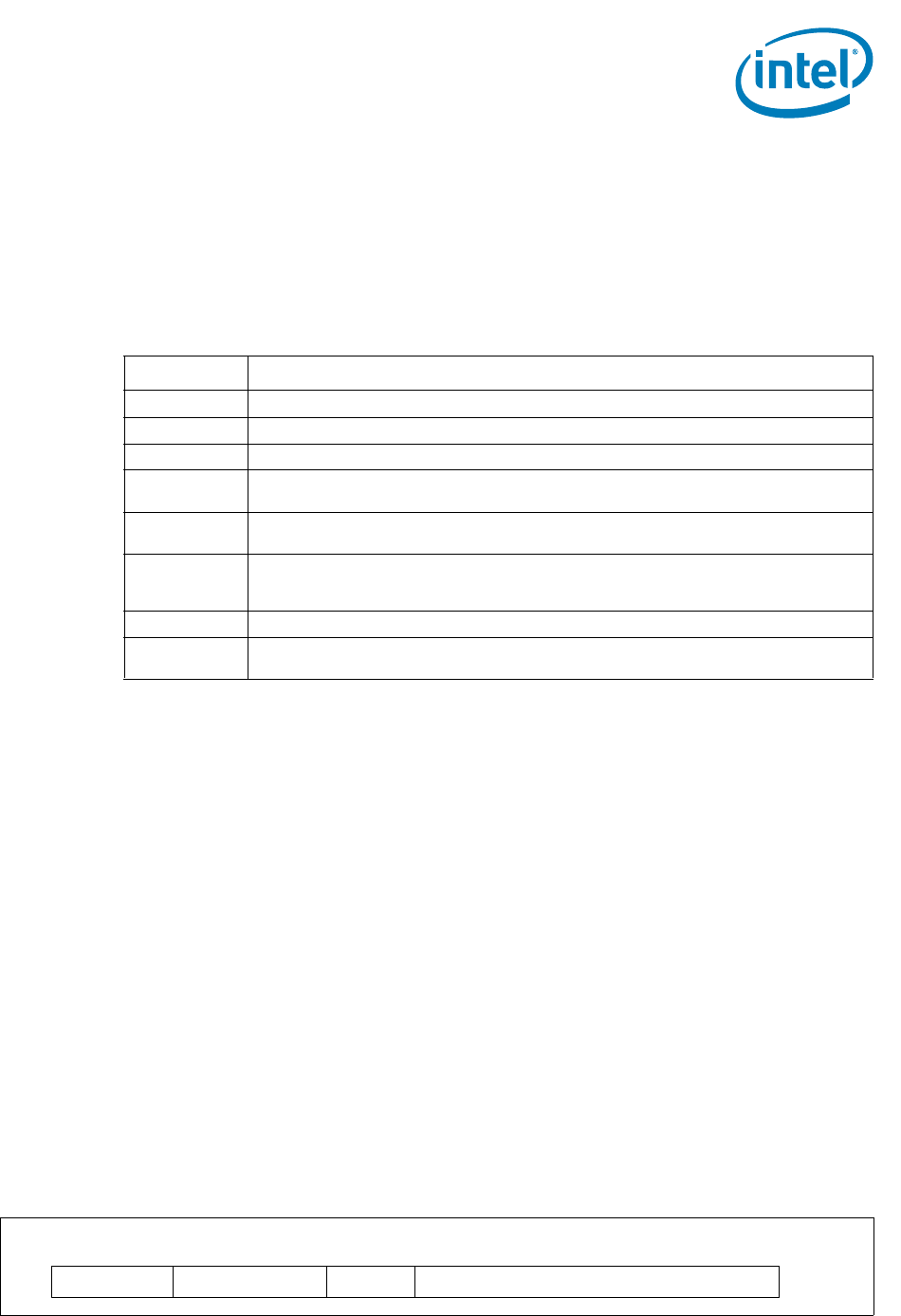

Table 2-12. RdPCIConfig() Response Definition

Response Meaning

Bad FCS Electrical error

Abort FCS Illegal command formatting (mismatched RL/WL/Command Code)

CC: 0x40 Command passed, data is valid.

CC: 0x80 Response timeout. The processor was not able to generate the required response in a

timely fashion. Retry is appropriate.

CC: 0x81 Response timeout. The processor is not able to allocate resources for servicing this

command at this time. Retry is appropriate.

CC: 0x82 The processor hardware resources required to service this command are in a low power

state. Retry may be appropriate after modification of PECI wake mode behavior if

appropriate.

CC: 0x90 Unknown/Invalid/Illegal Request

CC: 0x91 PECI control hardware, firmware or associated logic error. The processor is unable to

process the request.

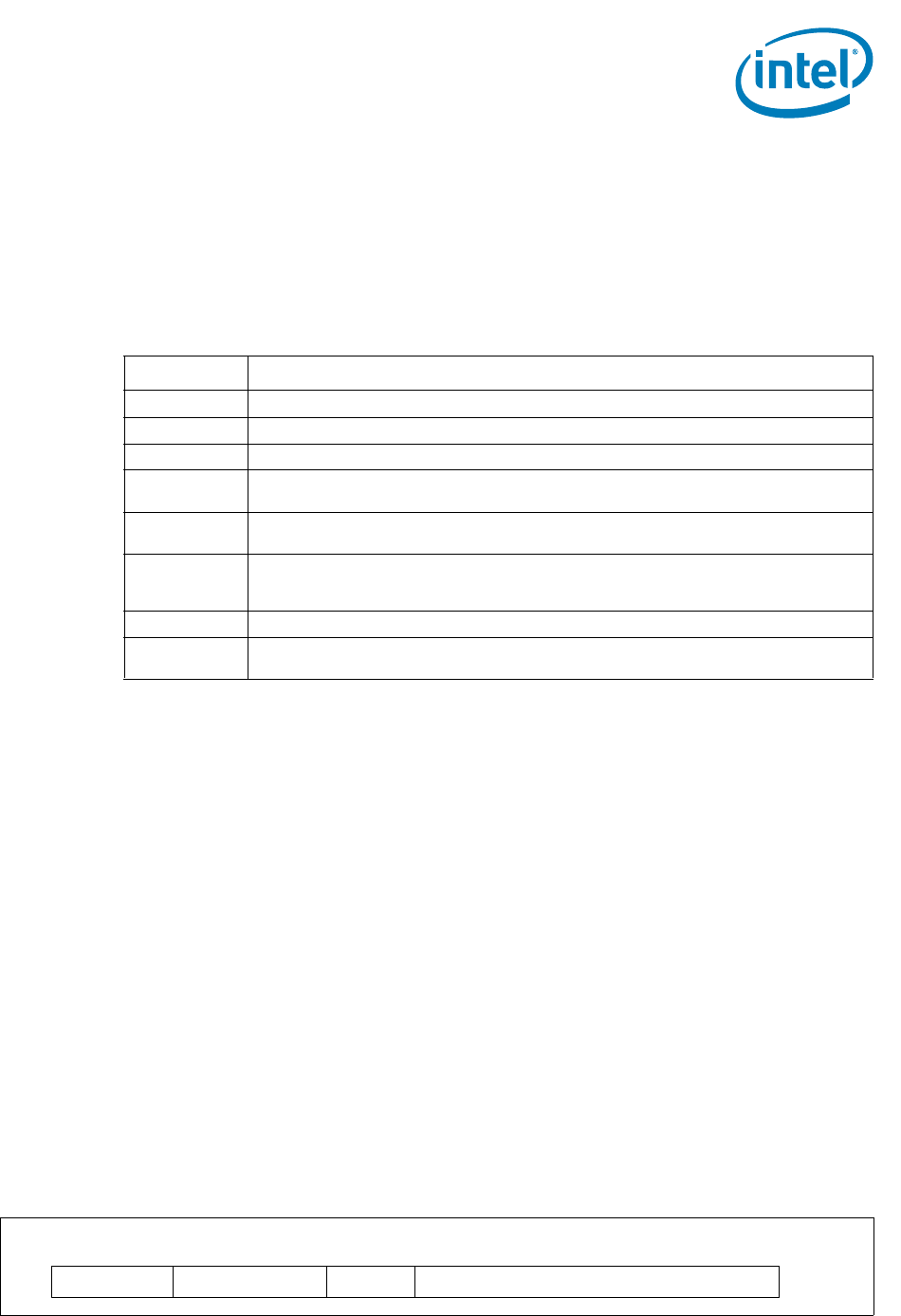

Figure 2-46. PCI Configuration Address for local accesses

20 19 15 1114 12 0

23

DeviceBus Function Register