39

4.6 Chipset Features Setup

This section allows you to configure the system based on the specific

features of the installed chipset. This chipset manages bus speeds and

the access to the system memory resources, such as DRAM and the

external cache. It also coordinates the communications between the

conventional ISA and PCI buses. It must be stated that these items

should never be altered. The default settings have been chosen

because they provide the best operating conditions for your system.

You might consider and make any changes only if you discover that the

data has been lost while using your system.

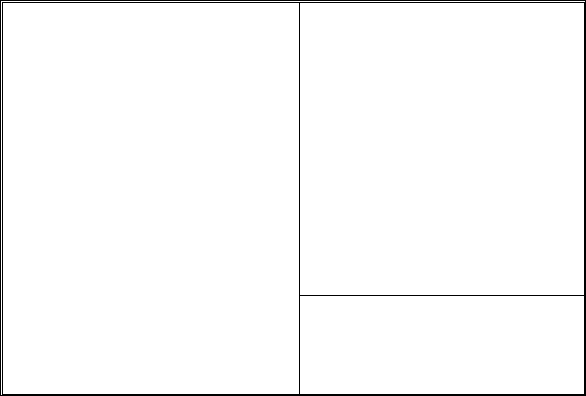

ROM PCI/ISA BIOS (2A69KD2L)

CHIPSET FEATURES SETUP

AWARD SOFTWARE, INC.

Auto Configuration : Enabled Power-Supply Type : Auto

EDO DRAM Speed Selection : 60ns Auto Detect DIMM/PCI Clk : Enabled

EDO CASx# MA Wait State : 2 Spread Spectrum : Disabled

EDO RASx# Wait State : 1 CPU Host Clock (CPU/PCI) : Default

SDRAM RAS-to-CAS Delay : 3 CPU Warning Temperature : Disabled

SDRAM RAS Precharge Time : 3 Current CPU Temperature

SDRAM CAS latency Time : 2 Shutdown Temperature : Disabled

SDRAM Precharge Control : Enabled

DRAM Data Integrity Mode : Non-ECC

System BIOS Cacheable : Enabled

Video BIOS Cacheable : Enabled

Video RAM Cacheable : Enabled

8 Bit I/O Recovery Time : 3

16 Bit I/O Recovery Time : 2

Memory Hole At 15M-16M : Disabled

Passive Release : Enabled ESC : Quit

: Select Item

Delayed Transaction : Disabled F1 : Help PU/PD/+/-: Modify

AGP Aperture Size (MB) : 64 F5 : Old Values (Shift) F2 : Color

F6 : Load BIOS Defaults

F7 : Load Setup Defaults

Auto Configuration:

Auto Configuration selects predetermined optimal values of

chipset parameters. When Disabled, chipset parameters revert to

setup information stored in CMOS. Many fields in this screen are

not available when Auto Configuration is Enabled. The available

choices are Enabled, Disabled.

EDO DRAM Speed Selection:

The DRAM timing is controlled by the DRAM Timing Registers.

The timings programmed into this register are dependent on the

system design. Slower rates may be required in certain system

designs to support loose layouts or slower memory.