KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 117 of 120 Ver. 0.9 KS152JB2

The SBUF sfr is set to 00h by a reset.

There is unrestricted read/write access to this SFR.

PORT 2

P2.7-0 Non-multiplexed address bus A15-A8: The port latch cannot be used for general I/O

purposes but exists to support the MOVX instructions. Port 2 data will only be

brought out on the P2.7-0 pins during indirect MOVX instructions.

The P2 sfr is set to FFh by a reset.

There is unrestricted read/write access to this SFR.

PORT 3

P3.7-0 General purpose I/O port. Each pin also has a alternate input or output function. This

alternate function is enabled if the corresponding port latch bit is set to 1, else the port

pin will remain stuck at 0.

P3.7

RD Strobe for read from external RAM

P3.6

WR Strobe for write to external RAM

P3.5 T1 Timer/counter 1 external count input

P3.4 T0 Timer/counter 0 external count input

P3.3

INT0 External interrupt 1

P3.2

INT1 External interrupt 0

P3.1 TxD Serial port output

P3.0 RxD Serial port input

The P3 sfr is set to FFh by a reset.

There is unrestricted read/write access to this SFR.

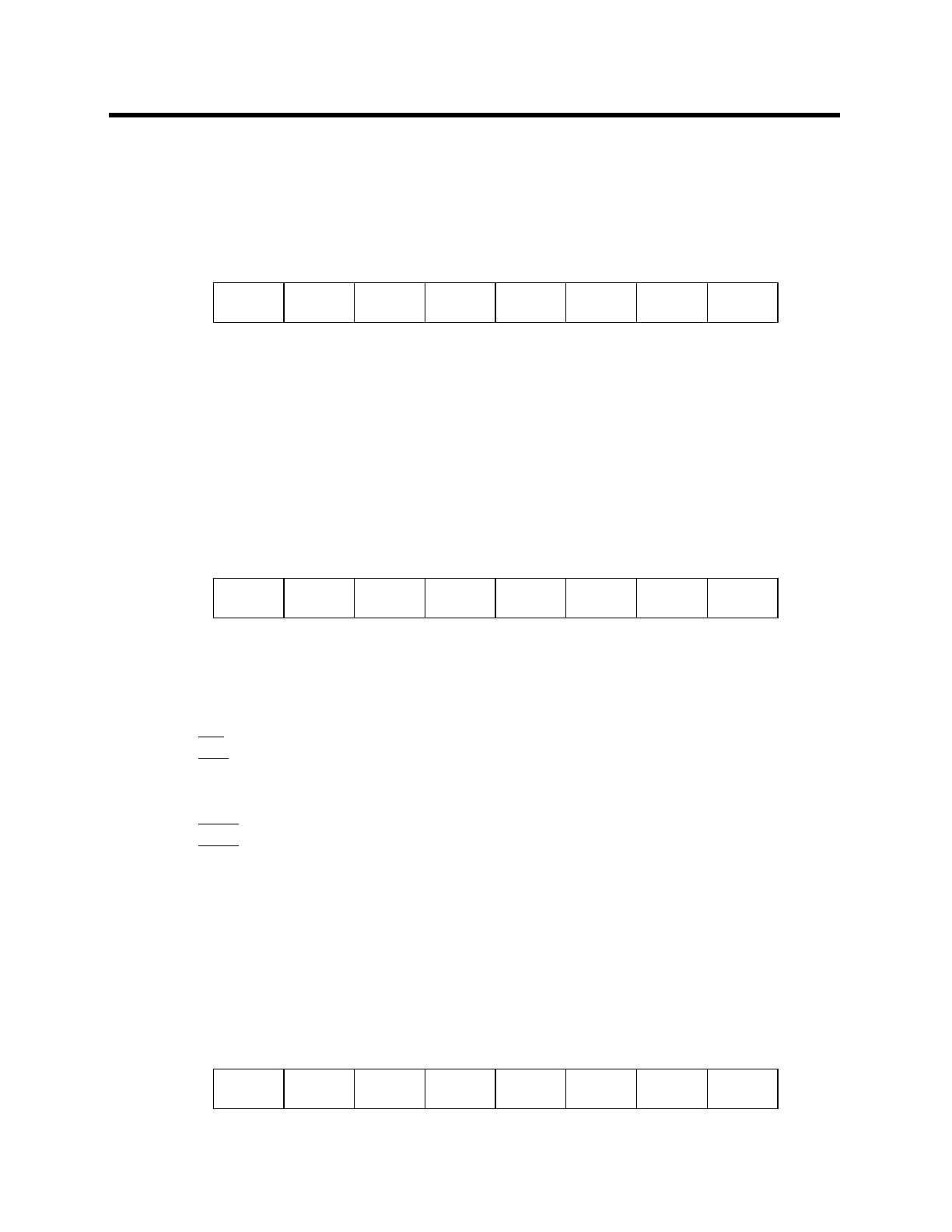

PROGRAM STATUS WORD

P2.6

6

P2.5

5

P2.3

3

P2.7

7

P2.2

2

P2.1

1

P2.0

0

P2.4

4

Bit:

Mnemonic: P2 Address: A0h

P3.6

6

P3.5

5

P3.3

3

P3.7

7

P3.2

2

P3.1

1

P3.0

0

P3.4

4

Bit:

Mnemonic: P3 Address: B0h

AC

6

F0

5

RS0

3

CY

7

OV

2

F1

1

P

0

RS1

4

Bit:

Mnemonic: PSW Address: D0h