KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 15 of 120 Ver. 0.9 KS152JB2

Mode 3 is used in cases where an extra 8 bit timer is needed. With Timer 0 in Mode 3, Timer 1 can

be turned on and off by switching it out of and into its own Mode 3. It can also be used as a baud

rate generator for the serial port.

2.8 Interrupts

The cpu has a provision for 11 different interrupt sources. These are the two external interrupts,

the three timer interrupts, the local serial port interrupt, dma interrupt and global serial port inter-

rupts.

The External Interrupts

INT0 and INT1 can be either edge triggered or level triggered, depending

on bits IT0 and IT1. The bits IE0 and IE1 in the TCON register are the flags which are checked to

generate the interrupt. When an interrupt is generated by these external interrupt inputs, they will

be cleared on entering the Interrupt Service routine, only if the interrupt type is edge triggered. In

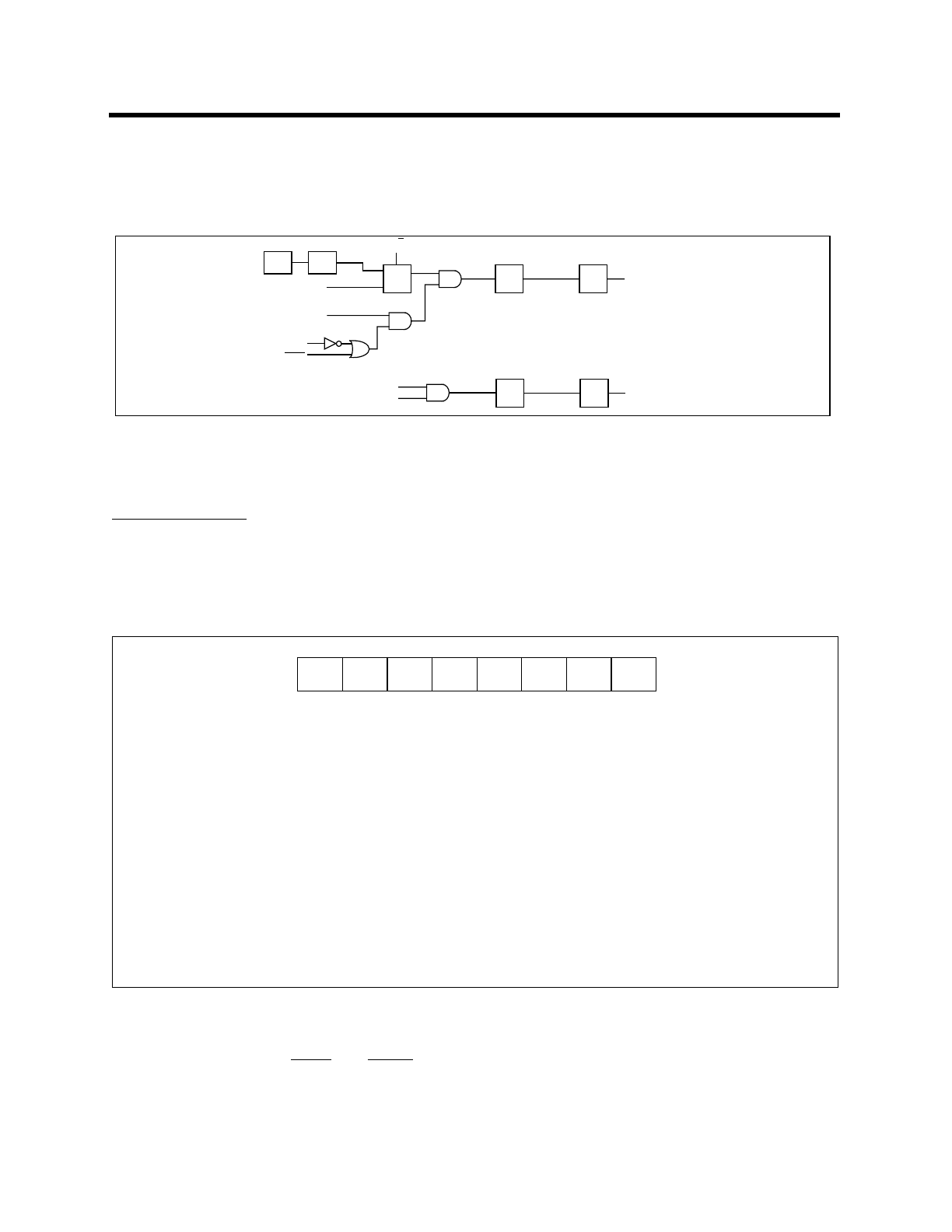

S3P1OSC

I0

I1

Q

GATE

INT0

pin

TR0

T0 pin

TL0

5 bits

TF0

INTERRUPT

C/T

Timer/Counter 0 in Mode 3

TH0

8 bits

TF1

INTERRUPT

S3P1

TR1

EA -- -- ES ET1 EX1 ET0 EX0

76543210

EA Global Disable bit. If this bit is cleared it disables all the interrupts at once.

IE: Interrupt Enable Register.

If EA is 1 then interrupts can be individually enabled/disabled by setting or

clearing its own enable bit.

reserved.--

EX0

ET0

EX1

ET1

ES

External interrupt 0 enable

Timer 0 interrupt enable.

External interrupt 1 enable.

Timer 1 interrupt enable.

Local Serial port interrupt enable.