8355 N/B MAINTENANCE

8355 N/B MAINTENANCE

100

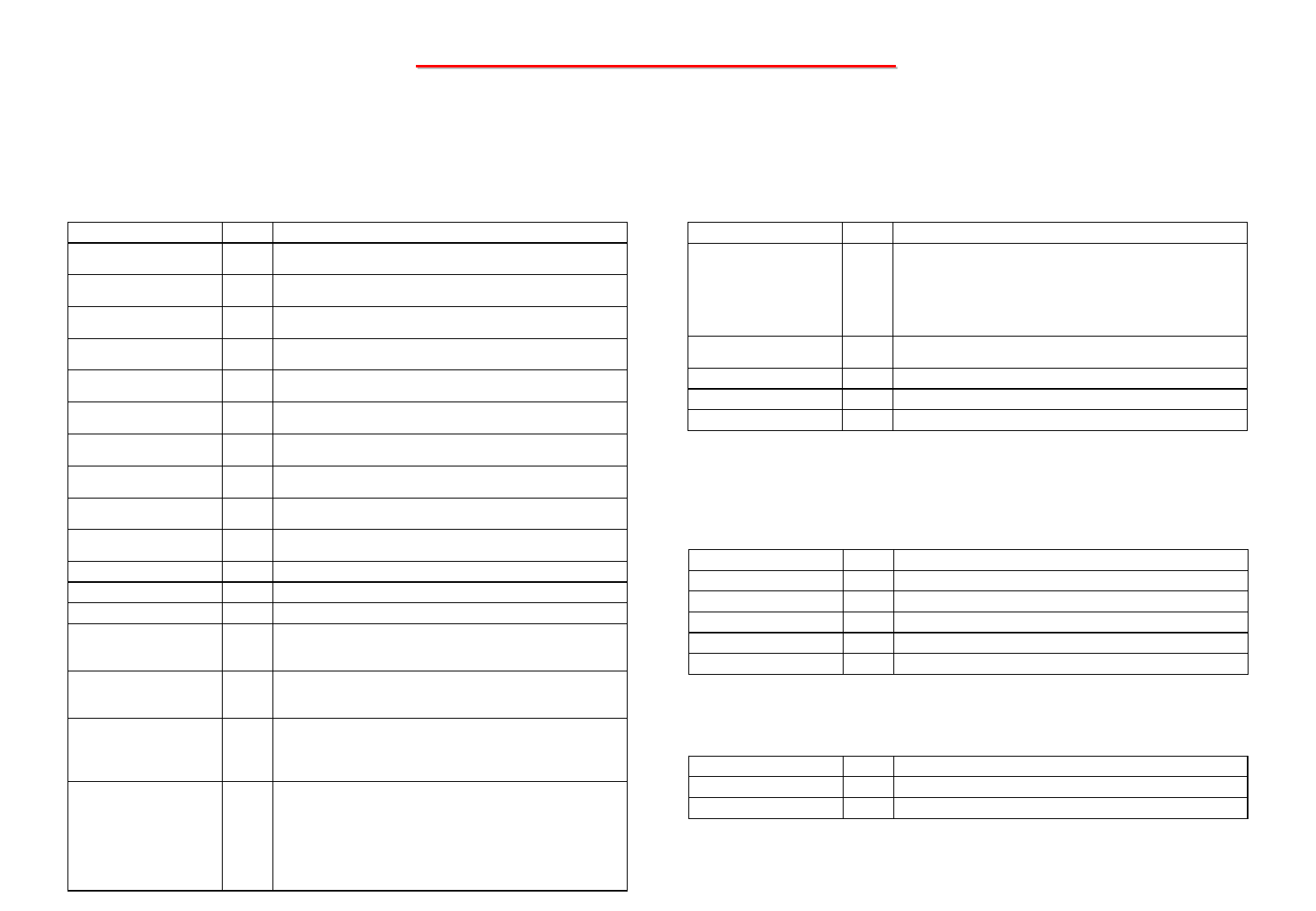

DDR SDRAM Memory Interface

Signal Name Type Description

MEMCLK_H/L[7]

O-IOD Differential DDR SDRAM clock to the top of DIMM 0 for

unbuffered DIMMs.

1

MEMCLK_H/L[6]

O-IOD Differential DDR SDRAM clock to the top of DIMM 0 for

unbuffered DIMMs.

1

MEMCLK_H/L[5]

O-IOD Differential DDR SDRAM clock to the bottom of DIMM 0 for

unbuffered DIMMs.

1

MEMCLK_H/L[4]

O-IOD Differential DDR SDRAM clock to the bottom of DIMM 0 for

unbuffered DIMMs.

1

MEMCLK_H/L[3]

O-IOD Differential DDR SDRAM clock to DIMM 3 for registered

DIMMs.

1

MEMCLK_H/L[2]

O-IOD Differential DDR SDRAM clock to DIMM 3 for registered

DIMMs.

1

MEMCLK_H/L[1]

O-IOD Differential DDR SDRAM clock to the middle of DIMM 1 for

unbuffered DIMMs, or DIMM 1 for registered DIMMs.

1

MEMCLK_H/L[0]

O-IOD Differential DDR SDRAM clock to the middle of DIMM 1 for

unbuffered DIMMs, or DIMM 1 for registered DIMMs.

1

MEMCKEA

MEMCKEB

O-IOS

Clock Enables to DIMMs. Used to gate clocks for power

management functionality.

1

MEMDQS[17:0]

B-IOS

DRAM Data Strobes synchronous with MEMDATA and

MEMCHECK during DRAM read and writes.

1

MEMDATA[63:0]

B-IOS DRAM Interface Data Bus

MEMCHECK[7:0]

B-IOS DRAM Interface ECC Check Bits

MEMCS_L[7:0]

O-IOS DRAM Chip Selects

1

MEMRASA_L

MEMRASB_L

O-IOS

DRAM Row Address Select. MEMRASA_L and

MEMRASB_L are functionally identical. Two copies are

provided to accommodate the loading of unbuffered DIMMs.

1

MEMCASA_L

MEMCASB_L

O-IOS

DRAM Column Address Select. MEMCASA_L and

MEMCASB_L are functionally identical. Two copies are

provided to accommodate the loading of unbuffered DIMMs.1

MEMWEA_L

MEMWEB_L

O-IOS

DRAM Write Enable. MEMWEA_L and MEMWEB_L are

functionally identical.

Two copies are provided to accommodate the loading of

unbuffered DIMMs.

1

MEMADDA[13:0]

MEMADDB[13:0]

O-IOS

DRAM Column/Row Address. Two copies are provided to

accommodate the loading of unbuffered DIMMs. During

precharges, activates, reads, and writes, the two copies

are inverted from each other (except A[10] which is used for

auto-precharge) to minimize switching noise. The signals are

inverted only when the bus is used to carry address

information.

1

DDR SDRAM Memory Interface Continue

Signal Name Type Description

MEMBANKA[1:0]

MEMBANKB[1:0]

O-IOS

DRAM Bank Address. Two copies are provided to

accommodate the loading of unbuffered DIMMs. During

precharges, activates, reads, and writes the two copies are

inverted from each other to minimize switching noise. The

signals are inverted only when the bus is used to carry address

information.

1

MEMRESET_L

O-IOS

DRAM Reset pin for Suspend-to-RAM power management

mode. This pin is required for registered DIMMs only.

MEMVREF

VREF DRAM Interface Voltage Reference

1

MEMZP

A Compensation Resistor tied to VSS

1

MEMZN

A Compensation Resistor tied to 2.5 V

1

Notes:

1. For connection details and proper resistor values, see the AMD Athlon™ 64 Processor Motherboard

Design Guide, order# 24665.

JTAG Pin Descriptions

Signal Name Type Description

TCK

I-IOS JTAG Clock

TMS

I-IOS JTAG Mode Select

TRST_L

I-IOS JTAG Reset

TDI

I-IOS JTAG Data Input

TDO

O-IOS JTAG Data Output

Clock

Signal Name Type Description

CLKIN_H/L

I-IOD 200-MHz PLL Reference Clock

FBCLKOUT_H/L

O-IOD Core Clock PLL 200-MHz Feedback Clock

5. Pin Descriptions of Major Components

5.1 AMD ATHLON

TM

64 Processor-1