8355 N/B MAINTENANCE

8355 N/B MAINTENANCE

113

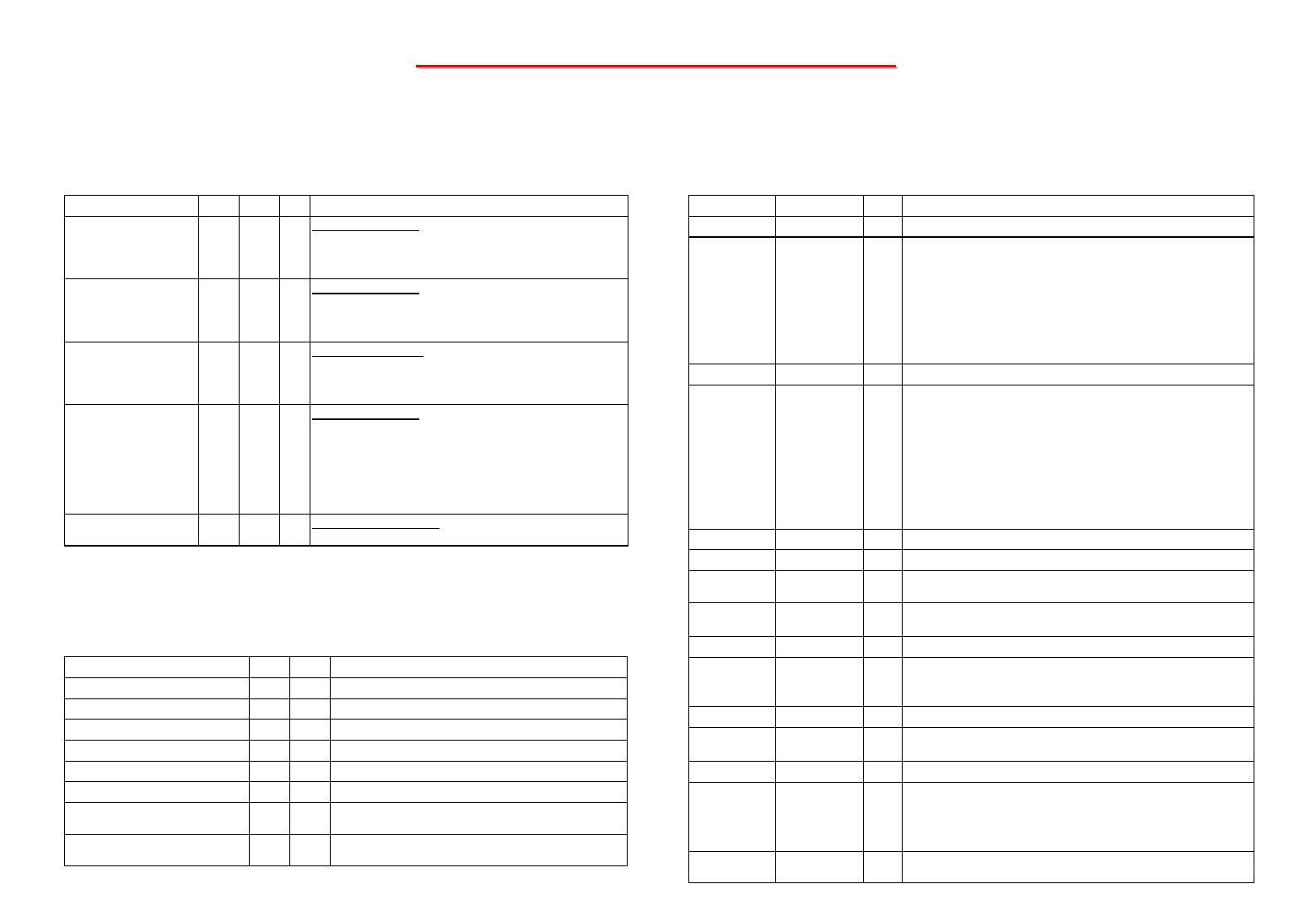

AC97 Audio /Modem Interface

Signal Name Pin # I/O Signal Description

ACRST# R3 O AC97 Reset.

ACBTCK T3 I AC97 Bit Clock.

ACSYNC T1 O AC97 Sync.

ACSDO U1 O AC97 Serial Data Out.

ACSDIN0 (VSUS33) T2 I AC97 Serial Data In 0.

ACSDIN1 (VSUS33) U3 I AC97 Serial Data In 1.

ACSDIN2 /GPIO20 /PCS0# U2 I AC97 Serial Data In2.RxE4[6]=0,E5[1]=0,PMIO

Rx4C[20]=1

ACSDIN3/GPIO21

/PCS1#/SLPBTN#

V1 I AC97 Serial Data In 3.RxE4[6]=0,E5[2]=0,PMIO

Rx4C[21]=1

The supply voltage for ACSDIN0-1 is VSUS33 so these inputs can support wake-up on modem ring

Internal Keyboard Controller

Signal Name Pin # I/O PU Signal Description

MSCK /IRQ1 W2 IO/I PU MultiFunction Pin (Internal mouse controller enabled by

Rx51[1]) Rx51[1]=1

Mouse Clock. From internal mouse

controller. Rx51[1]=0

Interrupt Request 1 .Interrupt

input 1.

MSDT /IRQ12 W1 IO/I PU MultiFunction Pin (Internal mouse controller enabled by

Rx51[1]) Rx51[1]=1

Mouse Data. From internal mouse

controller. Rx51[1]=0

Interrupt Request 12. Interrupt

input 12.

KBCK /KA20G V3 IO /I PU MultiFunction Pin (Internal keyboard controller enabled

by Rx51[0]) Rx51[0]=1 Keyboard Clock. From internal

keyboard controller Rx51[0]=0 Gate A20.Input from

external keyboard controller.

KBDT /KBRC V2 IO/I PU MultiFunction Pin (Internal keyboard controller enabled

by

Rx51[0])

Rx51[0]=1

Keyboard Data. From internal keyboard

controller.

Rx51[0]=0 Keyboard Reset. From external keyboard

controller (KBC)for CPURST# generation

KBCS#/ROMCS#/srap AF12 O/O Keyboard Chip Select (Rx51[0]=0).To external

keyboard controller chip. Strap high o enable LPC ROM:

Note: KBCK,KBDT,MSCK,and MSDT are powered by the VSUS33 suspend voltage plane.

Power and Ground

Signal Name Pin # I/O Signal Description

VCC33 (see pin list)v P

I/O Power.3.3V ±5%

VCC (see pin list) P

Core Power.2.5V ±5%.This supply is turned on only when he

mechanical switch on the power supply is turned on and he

PWRON signal is conditioned high .

Note: The VT8235L core voltage is 2.5V so board designs that

are intended t all w use of either VT8235 or VT8235L should

take this difference into account and allow the core voltage to

be selected as either 2.5V (for the VT8235)or 3.3V (for the

VT8235L).

GND (see pin list) P Ground. Connect o primary motherboard ground plane.

VSUS33 AA4,AB4,

AC4,AC5

P

Suspend Power.3.3V ±5%.Always available unless the

mechanical switch of the power supply is turned off. If the

“soft-off”state is not implemented, then this pin can be

Connected to VCC33.Signals powered by or referenced o this

plane are:PWRGD, RSMRST#,PWRBTN#,SMBCK1/2,

SMBDT1/2,GPO0,SUSA#/GPO1,SUSB#/ GPO2,SUSC#,

SUSST1#/GPO3,SUSCLK /GPO4,GPI1,GPI2/EXTSMI#,GPI3

/RING#,GPI4 /LID,GPI5 /BATLOW#,GPI6 /PME#,

SMBALRT#

VSUS25 T4,U4 P

Suspend Power.2.5V ±5%.

VSUSUSB D15 P

USB Suspend Power.2.5V ±5%.

VBAT AE4 P RTC Battery. Battery input for internal RTC

(RTCX1,RTCX2)

VLVREF J23 P

V-Link Voltage Reference.0.9V ±5%.0.34 xVCC25to0.38

xVCC25.

VCCVK (see pin list) P

V-Link Compensation Circuit Voltage.2.5V ±5%

MIIVCC D11,D12,

E11,E12

P

LAN MII Power.3.3V ±5%.Power for LAN Media

Independent Interface (interface to external PHY).Connect o

VCC33 through a ferrite bead.

MIIVCC25 D13,E13 P

LAN MII Suspend Power.2.5V ±5%.

RAMVCC E7 P

LAN RAM Power.2.5V ±5%.Power for LAN internal RAM.

Connect to VCC through a ferrite bead.

RAMGND E8 P LAN RAM Ground. Connect o GND through a ferrite bead.

USBVCC (see pin list) P

USB 2.0 Differential Output Power.3.3V ±5%.Power for

USB differential outputs (USBP0+,P0 –,P1+,P1 –,P2+,

P2 –, P3+, P3 –,P4+,P4 –,P5+,P5 –).Connect o VSUS33

through a ferrite bead.

USBGND (see pin list) P USB 2.0 Differential Output Ground. Connect to GND

through a ferrite bead.

5.3 VT8235 South Bridge-8