8355 N/B MAINTENANCE

8355 N/B MAINTENANCE

109

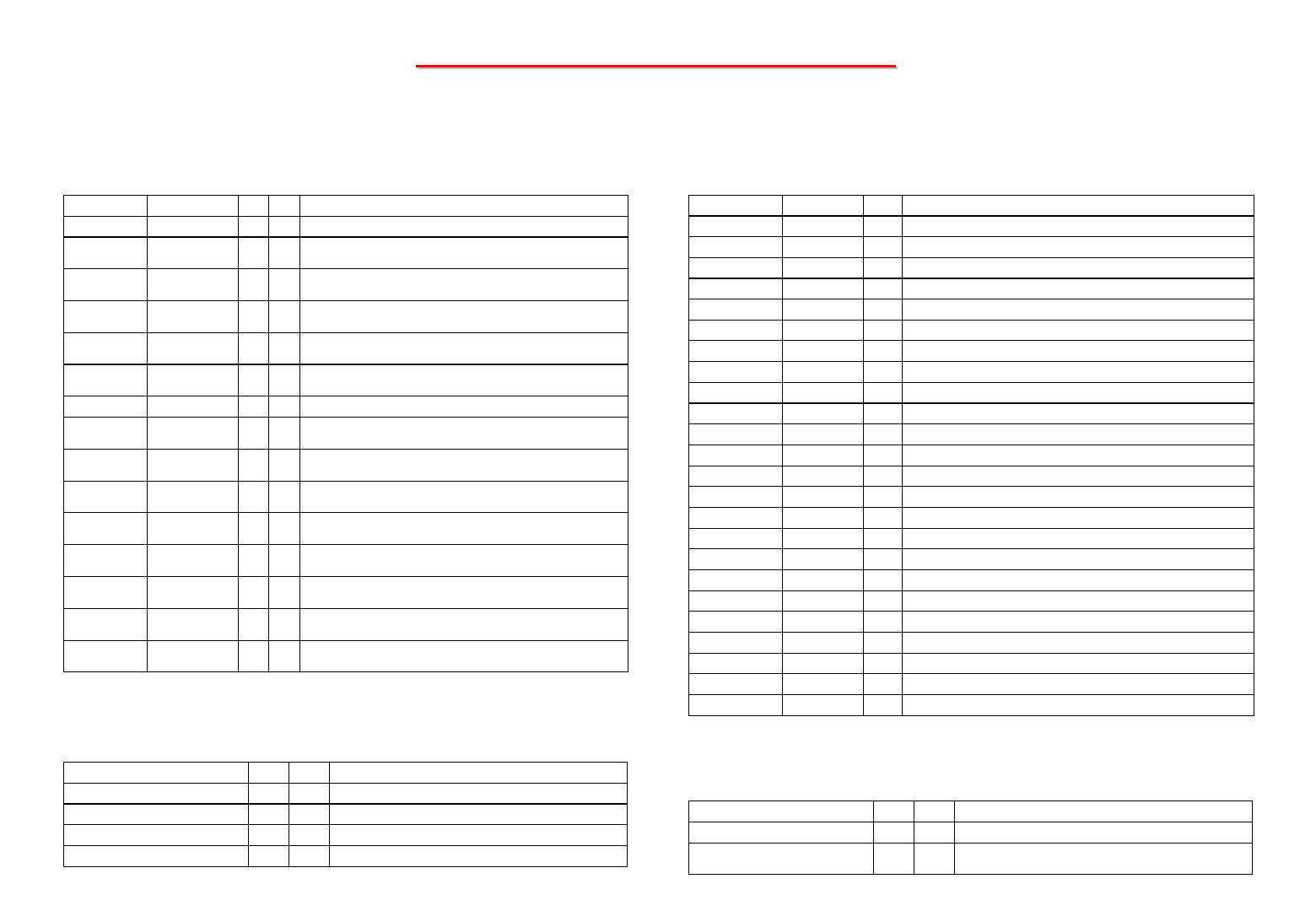

Universal Serial Bus 2.0 Interface

Signal Name Pin # I/O Signal Description

USBP0+ A21 IO USB 2.0 Port 0 Data +

USBP0 –

B21 IO

USB 2.0 Port 0 Data –

USBP1+ E21 IO USB 2.0 Port 1 Data +

USBP1 –

D21 IO

USB 2.0 Port 1 Data –

USBP2+ A19 IO USB 2.0 Port 2 Data +

USBP2 –

B19 IO

USB 2.0 Port 2 Data –

USBP3+ E19 IO USB 2.0 Port 3 Data +

USBP3 –

D19 IO

USB 2.0 Port 3 Data –

USBP4+ A17 IO USB 2.0 Port 4 Data +

USBP4 –

B17 IO

USB 2.0 Port 4 Data –

USBP5+ E17 IO USB 2.0 Port 5 Data +

USBP5 –

D17 IO

USB 2.0 Port 5 Data –

USBCLK D23 I USB 2.0 Clock.48MHz clock input for he USB interface

USBOC0# A15 I USB 2.0 Port 0 Over Current Detect. Port 0isdisablediflow.

USBOC1# B15 I USB 2.0 Port 1 Over Current Detect. Port1isdisablediflow.

USBOC2# C15 I USB 2.0 Port 2 Over Current Detect. Port2isdisablediflow.

USBOC3# E15 I USB 2.0 Port 3 Over Current Detect. Port 3isdisablediflow.

USBOC4# D14 I USB 2.0 Port 4 Over Current Detect. Port 4isdisablediflow.

USBOC5# E14 I USB 2.0 Port 5 Over Current Detect. Port 5isdisablediflow.

USBVCC (see pin list) Power USB 2.0 Port Differential Output Interface Logic Voltage.3.3V

USBGND (see pin list) Power USB 2.0 Port Differential Output Interface Logic Ground.

VSUSUSB D15 Power

USB 2.0 Suspend Power.2.5V

±5%.

VCCUPLL A23,D22 Power

USB 2.0 PLL Analog Voltage.2.5V

±5%.

GNDUPLL B23,E22 Power USB 2.0 PLL Analog Ground.

Programmable Chip Selects

Signal Name Pin # I/O Signal Description

PCS0#/GPIO20 /ACSDIN2 U2 O Programmable Chip Select 0.RxE4[6]=1,E5[1]=1

PCS1#/GPIO21/ACSDIN3

/SLPBTN#

V1 O Programmable Chip Select 1.RxE4[6]=1,E5[2]=1

LAN Controller -Media Independent Interface (MII)

Signal Name Pin # I/O PU Signal Description

MCOL C13 I PD MII Collision Detect. From he external PHY.

MCRS B13 I PD MII Carrier Sense. Asserted by the external PHY when the

media is active.

MDCK C9 O PD MII Management Data Clock. Sent to the external PHY as

a timing reference for MDIO

MDIO B9 IO PD MII Management Data I/O. Read from he MDI bit or

written to the MDO bit.

MRXCLK B10 I PD MII Receive Clock.2.5 or 25 MHz clock recovered by the

PHY.

MRXD[3-0] A9,D9,D10,E1

0

I PD MII Receive Data. Parallel receive data lines driven by the

external PHY synchronous with MRXCLK.

MRXDV C10 I PD MII Receive Data Valid.

MRXERR A10 I PD MII Receive Error. Asserted by the PHY when it detects a

data decoding error.

MTXCLK A12 I PD MII Transmit Clock. Always active 2.5 or 25 MHz clock

supplied by the PHY.

MTXD[3-0] C11,B11,A11,

C12

O PD MII Transmit Data. Parallel transmit data lines

synchronized to MTXCLK.

MTXENA B12 O PD MII Transmit Enable. Signals that transmit is active from

the MII port to the PHY.

MIIVCC D11,D12,E11,

E12

Pow

er

MII Interface Power.3.3V ±5%.

MIIVCC25 D13,E13 Pow

er

MII Suspend Power.2.5V ±5%.

RAMVCC E7 Pow

er

Power For Internal LAN RAM.2.5V ±5%.

RAMGND E8 Pow

er

Ground For Internal LAN RAM.

General Purpose I/O

Signal Name Pin # I/O Signal Description

GPIOA /GPI24/GPO24 AE5 IO General Purpose I/O A /24. RxE6[0]=1

GPIOC /GPI25/GPO25 AE6 IO General Purpose I/O C /25.

GPIOD /GPI30/GPO30 AD6 IO

General Purpose I/O D /30.

GPIOE /GPI31/GPO31 AC6 IO

General Purpose I/O E /31.

The output type of he above pins may be selected as either OD or TTL (see Device 17 Function 0 RxE7)

5.3 VT8235 South Bridge-4