8355 N/B MAINTENANCE

8355 N/B MAINTENANCE

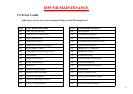

110

UltraDMA-133 /100 /66 /33 Enhanced IDE Interface

Signal Name Pin # I/O Signal Description

PDRDY /

PDDMARDY

/

PDSTROBE

Y26 I EIDE Mode: Primary I/O Channel Ready.Device read indicator

UltraDMA Mode:Primary Device DMA Ready .Output flow control.

The device may assert DDMARDY o pause output

transfers Primary Device Strobe .Input data strobe

(both edges).The device may s op DSTROBE to

pause input data transfers

SDRDY /

SDDMARDY

/

SDSTROBE

AD15 I EIDE Mode: Secondary I/O Channel Ready. Device ready

indicator

UltraDMA Mode: Secondary Device DMA Ready .Output flow

control. The device may assert DDMARDY to

pause output transfers Secondary Device

Strobe .Input data strobe (both edges).The

device may stop DSTROBE o pause input data

transfers

PDIOR#/

PHDMARDY

/

PHSTROBE

Y24 O EIDE Mode: Primary Device I/O Read. Device read strobe

UltraDMA Mode: Primary Host DMA Ready .Primary channel

input flow control .The host may assert

HDMARDY o pause input transfers Primary

Host Strobe .Output data strobe (both

edges).The host may stop HSTROBE o pause

output data transfers

SDIOR#/

SHDMARDY

/

SHSTROBE

AF22 O EIDE Mode: Secondary Device I/O Read. Device read strobe

UltraDMA Mode: Secondary Host DMA Ready .Input flow control.

The host may assert HDMARDY to pause input

transfers Host Strobe B .Output strobe (both

edges).The host may stop HSTROBE to pause

output data transfers

PDIOW#/

PSTOP

Y25 O EIDE Mode: Primary Device I/O Write. Device wri te

strobe

UltraDMA Mode: Primary Stop.Stop transfer: Asserted by the

host prior to initiation an UltraDMA burst;

negated by the host before data is transferred an

UltraDMA burst. Assertion of STOP by he host

during or after transfer in UltraDMA mode

signals the nation of the burst

SDIOW#/

SSTOP

AC21 EIDE Mode: Secondary Device I/O Write.Device writ strobe

UltraDMA Mode: Secondary Stop .Stop transfer Asserted by the

host prior to initiation of an UltraDMA

burst;negated by the host before data is

transferted in an ULtraDMA burst Assert of

Stop by the host during or after data transfer in

ULtraDMA mode signals the termination of the

burst

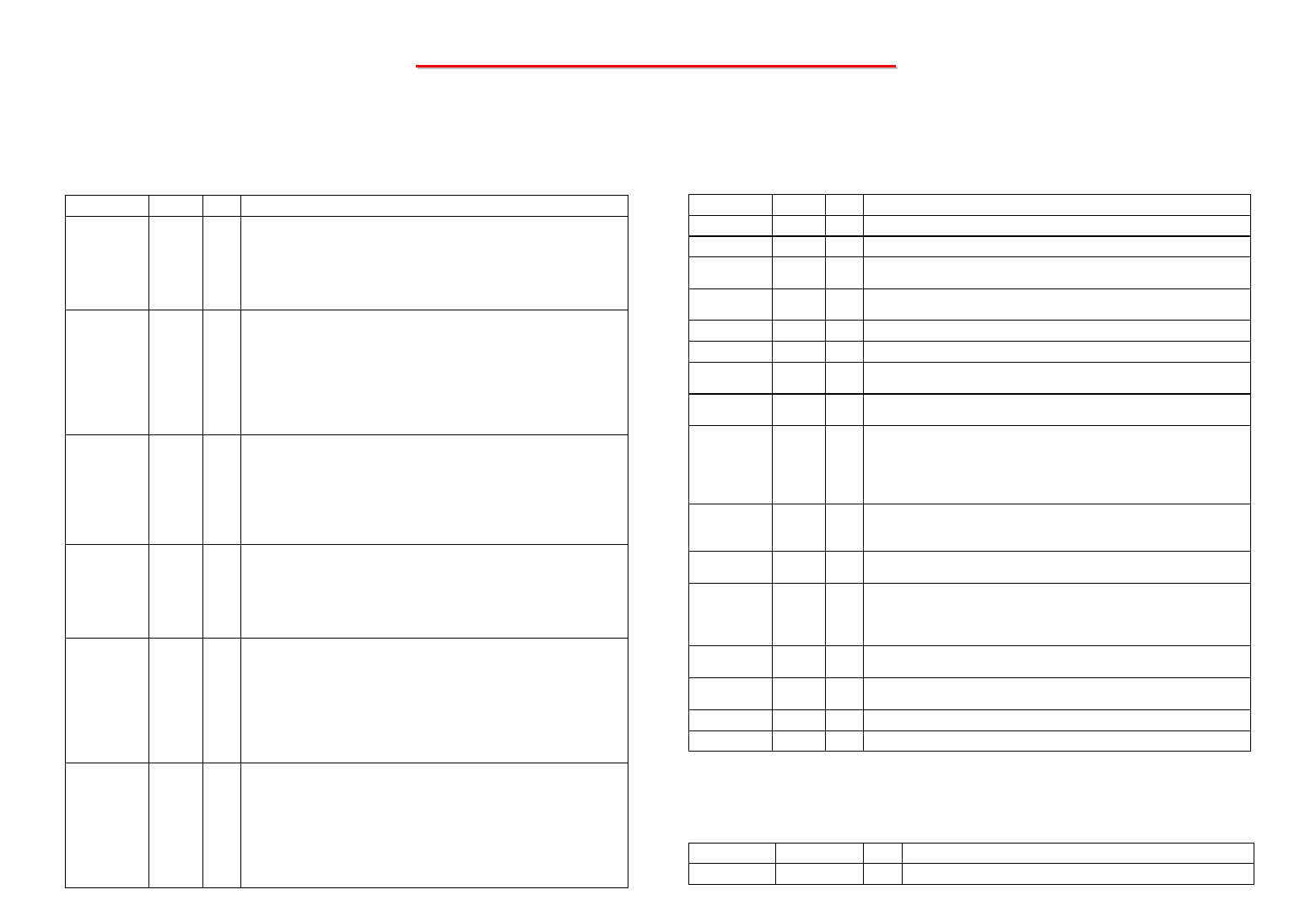

UltraDMA-133 /100 /66 /33 Enhanced IDE Interface Continue

Signal Name Pin # I/O Signal Description

PDDRQ Y22 I Primary Device DMA Request.Primary channel DMA request

SDDRQ AE15 I Secondary Device DMA Request.Secondary channel DMA request

PDDACK# W26 O Primary Device DMA Acknowledge.Primary channel DMA

acknowledge

SDDACK# AD22 O Secondary Device DMA Acknowledge.Secondary channel DMA

acknowledge

IRQ14 AE24 I Primary Channel Interrupt Request.

IRQ15 AF24 I Secondary Channel Interrupt Request.

PDCS1# V24 Primary Master Chip Select.This signal corresponds toCS1FX#on the

primary IDM connector

PDCS3# W24 Primary Slave Chip Select.This signal corresponds to CS3FX# on the

primary IDE connector.

SDCS1#/srap AC23 Secondary Master Chip Select.This signal corresponds o CS17X# on

he secondary IDE connector.S rap low (resistor o ground) to enable

serial EEPROM interface via he MII bus (this disables the EExx

pins).This pin has an internal pullup to default to serial EEPROM

interface via the EEPROM interface via the Eexx pine

SDCS3#/s rap AD23 Secondary Slave Chip Select. This signal corresponds toCS37X#on

the secondary IDE connector. Strap information is communicated to

the north bridge via VAD[7].

PDA[2-0] V26,V2

5,Y23

Primary Disk Address. PDA[2:0]are used o indicate which by e in

either the ATA command block or control block is being accessed.

SDA[2-0]/s

rap

AF23,A

C22,AE

23

Secondary Disk Address. SDA[2:0]are used o indicate which

byte in either the ATA command block or control block is being

accessed. Strap information is communicated to the north bridge via

VAD[6:4].

PDD[15-0] (see pin

list)

Primary Disk Data.

SDD[15-0]/S

A[15-0]

(see pin

list)

Secondary Disk Data.

PDCOMP W23 Primary Disk Compensation.

SDCOMP AC15 Secondary Disk Compensation.

Serial IRQ

Signal Name Pin # I/O Signal Description

SERIRQ AE10 I Serial IRQ. This pin has an internal pull-up resistor.

5.3 VT8235 South Bridge-5