8355 N/B MAINTENANCE

8355 N/B MAINTENANCE

105

5.2 K8T800M(VT8385) North Bridge-4

Clock, Reset, Power Control and Test

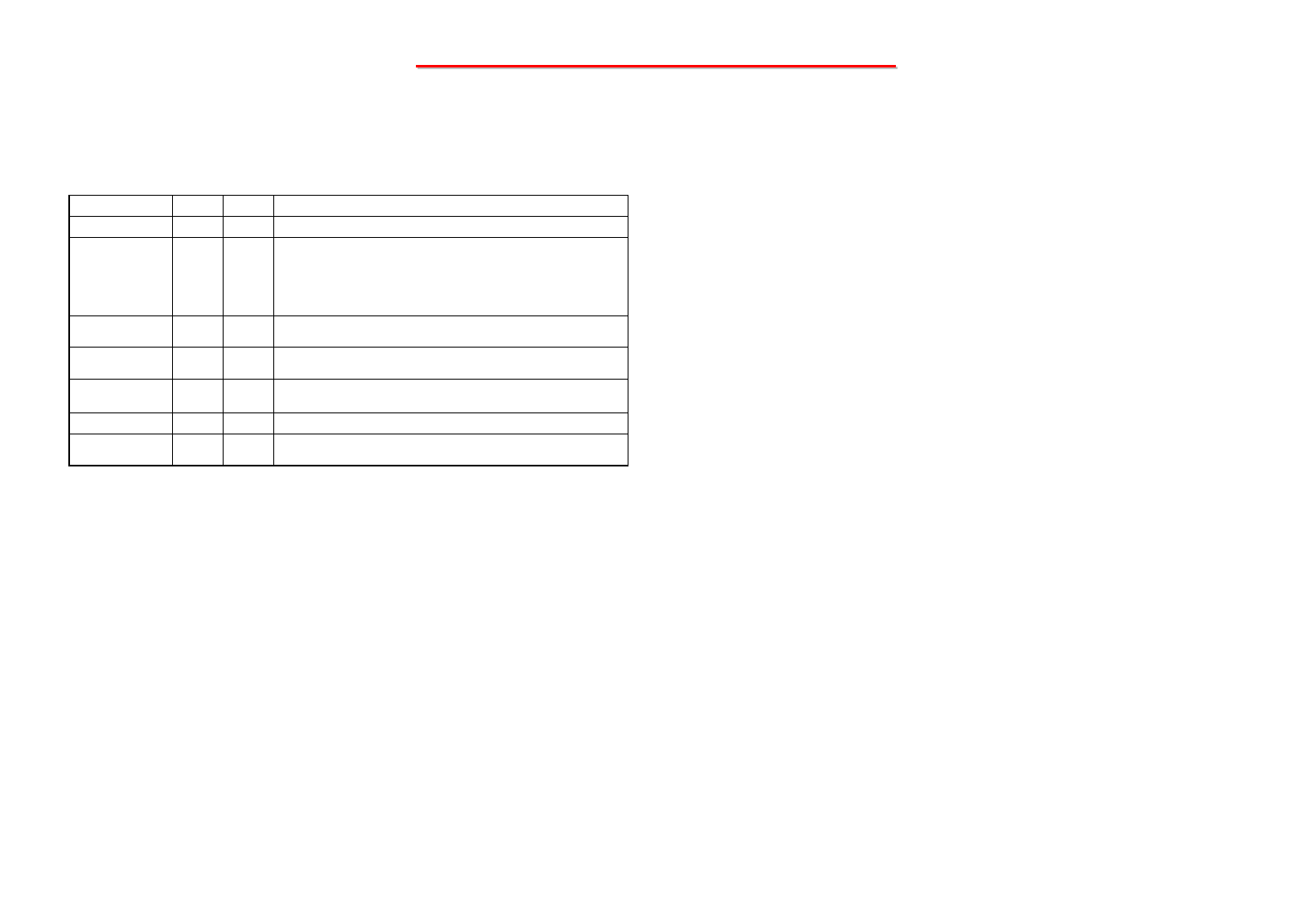

Signal Name Type I/O Description

GCLK

A11 I AGP Clock. 66 MHz clock for AGP logic.

RESET#

AD25 I Reset. Input from the south Bridge chip. 3.3V tolerant input.

When asserted, this signal resets the chip and sets all register

bits to the default value. The rising edge of this signal is used to

sample all power-up strap options. In addition, HTRST# is

driven active to reset the K8 CPU.

PWROK

AE26 I Power Ok. Driven by South Bridge PWROK output from the

power supply PWRGOOD input to PULL-up to disable.

SUSST

AD26 I Suspend Status. For implementation of the Suspend-to-DRAM

feature. Connect to an external pull-up to disable.

TESTIN

AC26 I Test In. This pin is used for terssting and must be left

unconnected or tied high (4.7KΩ to 2.5V) on all board designs.

DEBUG AC17 Debug.

NC (see pin

list)

No Connect. Reserved for graphics functions in pin-compatible

“K8M800” chipset north bridge.