8355 N/B MAINTENANCE

8355 N/B MAINTENANCE

114

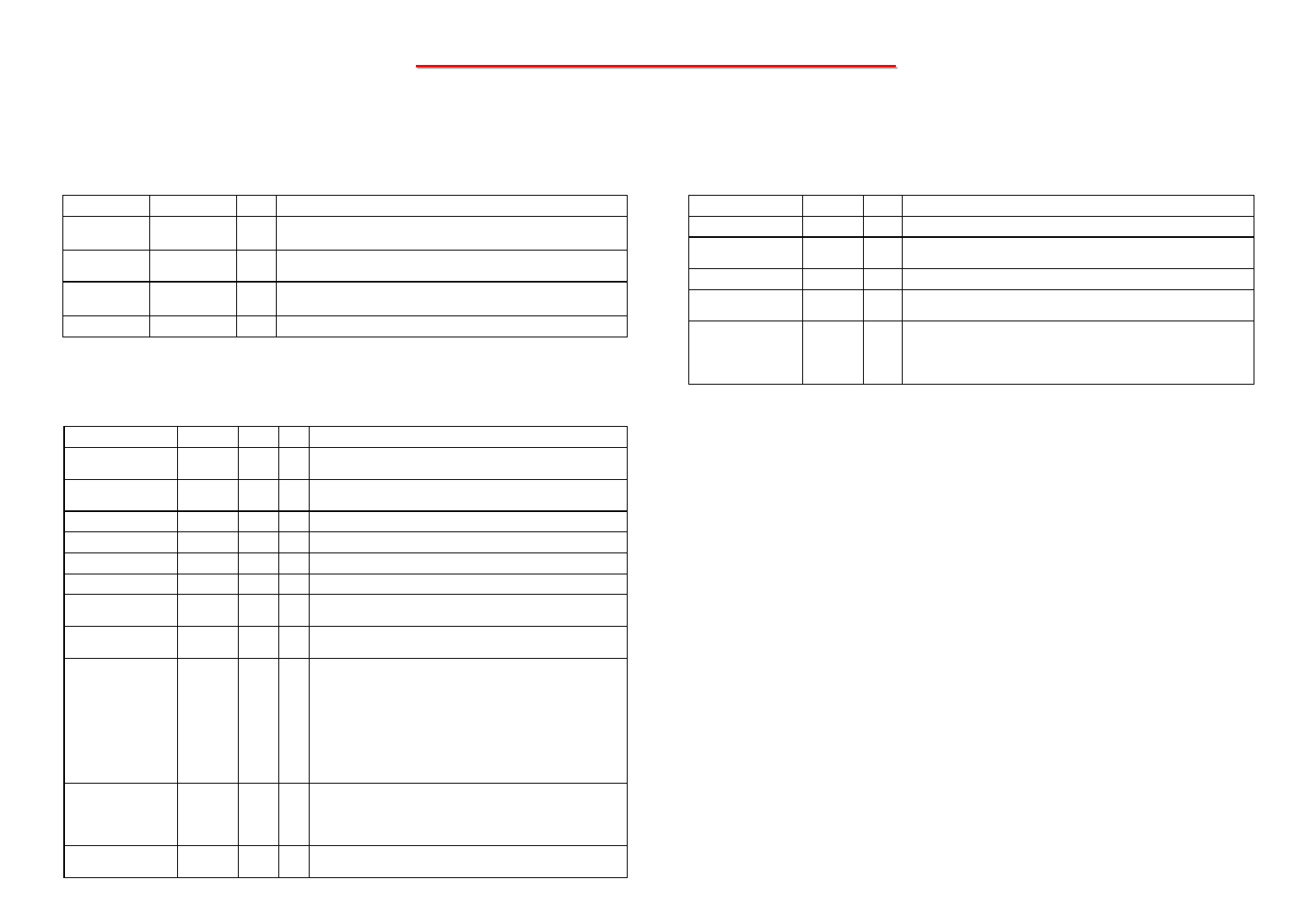

System Management Bus (SMB)Interface (I 2 CBus)

Signal Name Pin # I/O Signal Description

SMBCK1 AB3 IO SMB /I

2

C Channel 1 Clock.

SMBCK2

/GPI27/GPO27

AE1 IO SMB /I

2

C Channel 2 Clock.Rx95[2]=0

SMBDT1 AC2 IO SMB /I

2

C Channel 1 Data.

SMBDT2

/GPI26/GPO26

AD1 IO SMB /I

3

C Channel 2 Data.Rx95[2]=0

SMBALRT# AB2 I SMB Alert.(enabled by System Management Bus I/O space

Rx08[1]When the chip is enabled to allow it, assertion

generates an IRQ SMI interrupt or a power management resume

event. Connect o a ohm pull up to VSUS33 if not used.

Power and Ground Continue

Signal Name Pin # I/O Signal Description

VCCUPLL A23,D22 P

USB 2.0 PLL Analog Voltage.2.5V

±5%.Connect to VCC

through a ferrite bead.

GNDU

PLL

B23,E22 P USB 2.0 PLL Analog Ground. Connect to GND through a

ferrite bead.

PLLVCC P22 P

PLL Analog Power.2.5V

±5%.Connect to VCC through a

ferrite bead.

PLLGND P23 P PLL Analog Ground. Connect o GND through a ferrite bead.

ISA Subset /Parallel BIOS ROM Interface

Signal Name Pin # I/O PU Signal Description

ROMCS#/KBCS#/

strap

AF12 O ROM Chip Select (Rx51[0]=1).Chip Select o the BIOS

ROM. Strap high to enable LPCROM.

SPKR /srap AE9 O Speaker. Strap low to enable (high o disable)CPU

frequency strapping.

MEMR# AE12 O

Memory Read.

MEMW# AF10 O

Memory Write.

IOR# AC10 O

I/O Read.

IOW# AD9 O

I/O Write.

IORDY /GPI19 AD10 I I/O Ready. Used to insert wait states in I/O or memory

cycles. RxE5[0]=0

SOE#/s rap AD12 O XD Bus Tranceiver Output Enable. Strap low to enable

auto reboot.

XD[7-0] AD13,AE

13,

AF13,AD

14,

AE14,AF

14,

AC13,AC

14

IO XD Bus. For input of BIOS ROM data or data from to

her on-board I/O or memory devices.

SA[19-16]/GPO[19

-16]

/sraps

AC11,AD

11,

AE11,AF

11

O PD System Address 19-16.Strap states are passed to North

Bridge via VAD[3-0].Functions as SA[19-16]if

RxE4[5]=0.

SA[15-0]/SDD[15-

0]

(see pin

lis )

O System Address 15-0.

5.3 VT8235 South Bridge-9