8355 N/B MAINTENANCE

8355 N/B MAINTENANCE

103

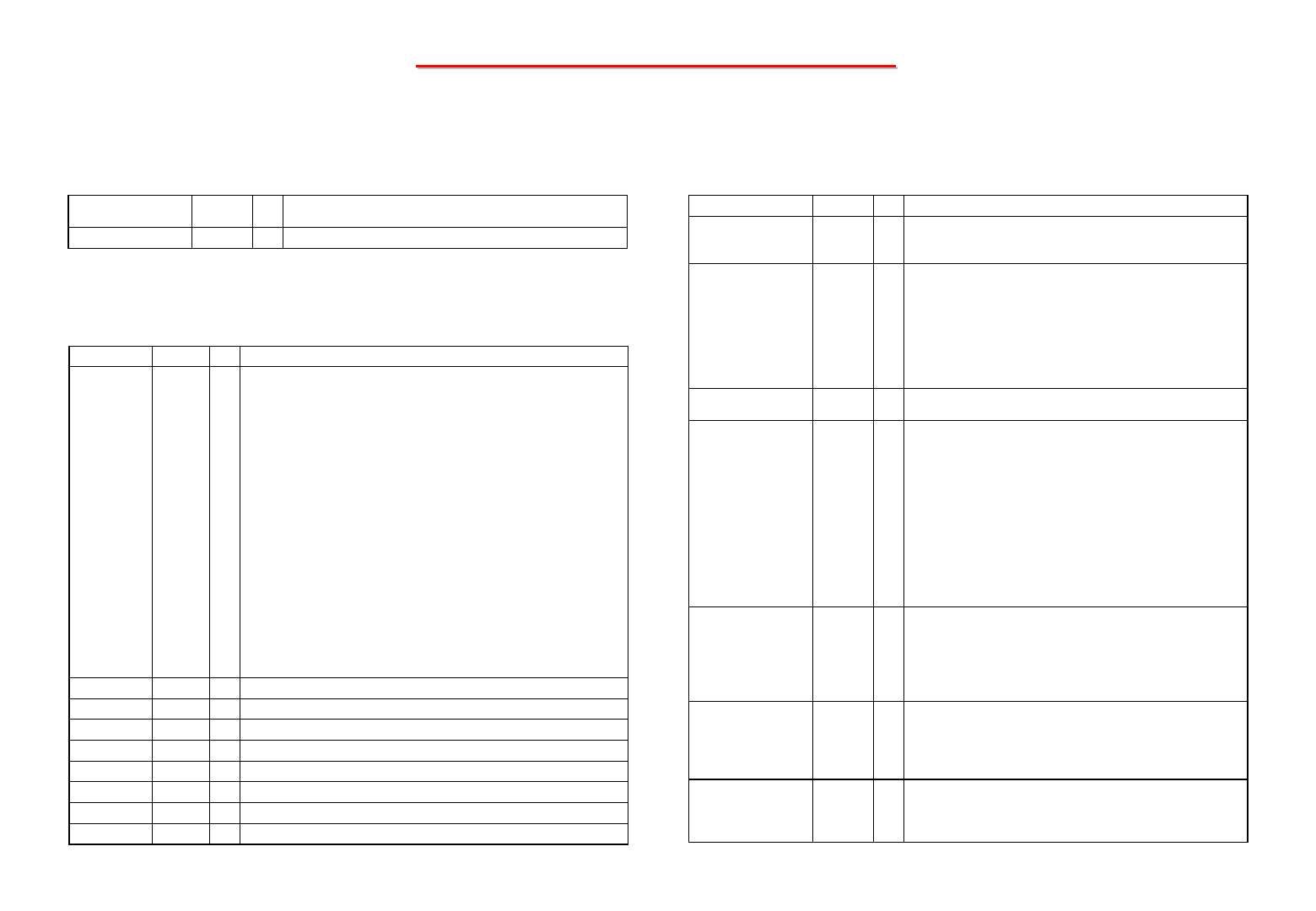

“Hyper Transport” Control

HTRST#

B11 O Hyper Transport Reset.Connect to RESET# pin of K8

CPU.2.5V swing.Active when the RESET# input is active

HTSTP#

A12 I Hyper Transport Stop. Connect to South Bridge DPSLP# pin

V-Link Interface

Signal Name Type I/O Description

VAD7,

VAD6

VAD5

VAD4

VAD3

VAD2

VAD1,

VAD0

AF25

AD24

AF20

AE19

AE24

AF24

AD21

AD20

IO

IO

IO

IO

IO

IO

IO

IO

Address/Data Bus.Also used to pass strap information from the south

bridge to the north bridge (the physical strap is not on the north bridge

VAD pin of the south bridge with the information passed over to the

north bridge at reset time)

Connection Register SB Pin

VAD7-Test Mode L=Disable, n/a SDCS3#

H=Enable

VAD6-ROMSIP L=Disable, Rx51[7] SDA2

H=Enable

VAD5-Loop Test Mode L=Disable, n/a SDA1

H=Enable

VAD4-reserved n/a n/a SAD0

VAD3-Fast Command L=Disable, Rx53[7] SA19

H=Enable

VAD2-HT Bus Width L=8 bits, n/a SA18

H=16 bits

VAD1-HT Bus Frequency Msb LL=200MHz RxCC[9] SA17

LH=400MHz

VAD0-HT Bus Frequency Lsb LL=600MHz RxCC[8] SA16

LH=800MHz

VPAR

AF19 IO Parity

VBE#

AE21 IO Byte Enable

UPCMD

AF26 I Command from Client(South Bridge) to Host(North Bridge)

UPSTB

AE23 I Strobe from Client to Host

UPSTB#

AF23 I Complement Strobe form Client to Host

DNCMD

AD23 O Command from Host(North Bridge) to Client(South Bridge)

DNSTB

AF22 O Strobe from Host to Client

DNSTB#

AD22 O Complement Strobe form Host to Client

AGP Bus Interface

Signal Name Type I/O Description

GD[31:0]

(See pin

list

IO Address / Data Bus. Address is deiven with GDS assertion for

AGP-style transfers and with GFRM# assertion for PCI-stle

trafers.

GBE[3:0]

(GBE[3:0#] for 4x

mode

AC7

AD11

AF11

AD11

IO

Command /byte Enable (interpreted as C/BE# for AGP 2x/4x

And (C# /BE# for PCI ) driven by the master (graphics

controller) when requests are being enqueued using GPIPE#

2x/4x only as GPIPE# isn’t used in 8x mode). These pin

provide valide byte information during AGP write transaction

And are driven by master. Thfe target (this chip) drives these

line to “0000” during the return of AGP read data. For PCI

cycles, commands are driven on gollowing clocks

GPAR

AC16 IO AGP Parity A single parity bit is provided over GD[31:0]

and GBE[3:0]..

GDBIH /GPIPE#

GDBIL

AC5

AC4

IO Dynamic Bus inversion High /Low. AGP 8x transfer mode

only. Driven by the source to indicate whether the

corresponding data bit group should be inverted). Used to

limit thenamber of simultaneously switching outputs to 8 for

each 16-pin group.

Pipelined Request. Not used by AGP 8x. Asserted by the

master external graphics the master enqueues one request is to

be enqueued by the target (North bridge ) The master

enqueues one request each rising edge of GCLK while

GPIPE# is asserted. When GPIPE# is deasserted no new

requests are enqueued across the AD bus

Note: See RxAE[1] for GPIPE# GDBIH pin function selection

GDS0F (GDS0 for

4x)

GDS0S (GDS0# for

4x)

AE15

AF15

IO Bus Strobe 0. Source synchronous strobes for GD[15:0] (the

agent that is providing the data drives these signals) GDS0

provides timing for 2x data transfer mode: GDS0 and GDS0#

Provide timing for 4x mode. For 8x transfer mode, GDS0 is

interpreted as GDS0F (“First strobe) and GDS0# as

GDS0S(“second” strobe )

GDS1F (GDS1 for

4x)

GDS1S GDS1# for

4x)

AE7

AF7

IO Bus Strobe 1. Source synchronous strobes for GD[31:16] (i.

e , the agent that is providing the data drives these signals ).

GDS1 provides timing for 2x data transfer mode: GDS1 and

GDS1F (“first” strobe) and GDS1# as GDSIS (“second”

strobe)

GFRM (GFRM# for

4x)

AC9 IO Frame. Assertion indicates the address phase of a PCI/ transfer

. Negation indicates that one more date transfer is desired by

the cycle initiator interpreted as active high for AGP 8x.

5.2 K8T800M(VT8385) North Bridge-2