User Interfaces DMD15/DMD15L IBS/IDR Satellite Modem

4-88 TM051 – Rev. 5.8

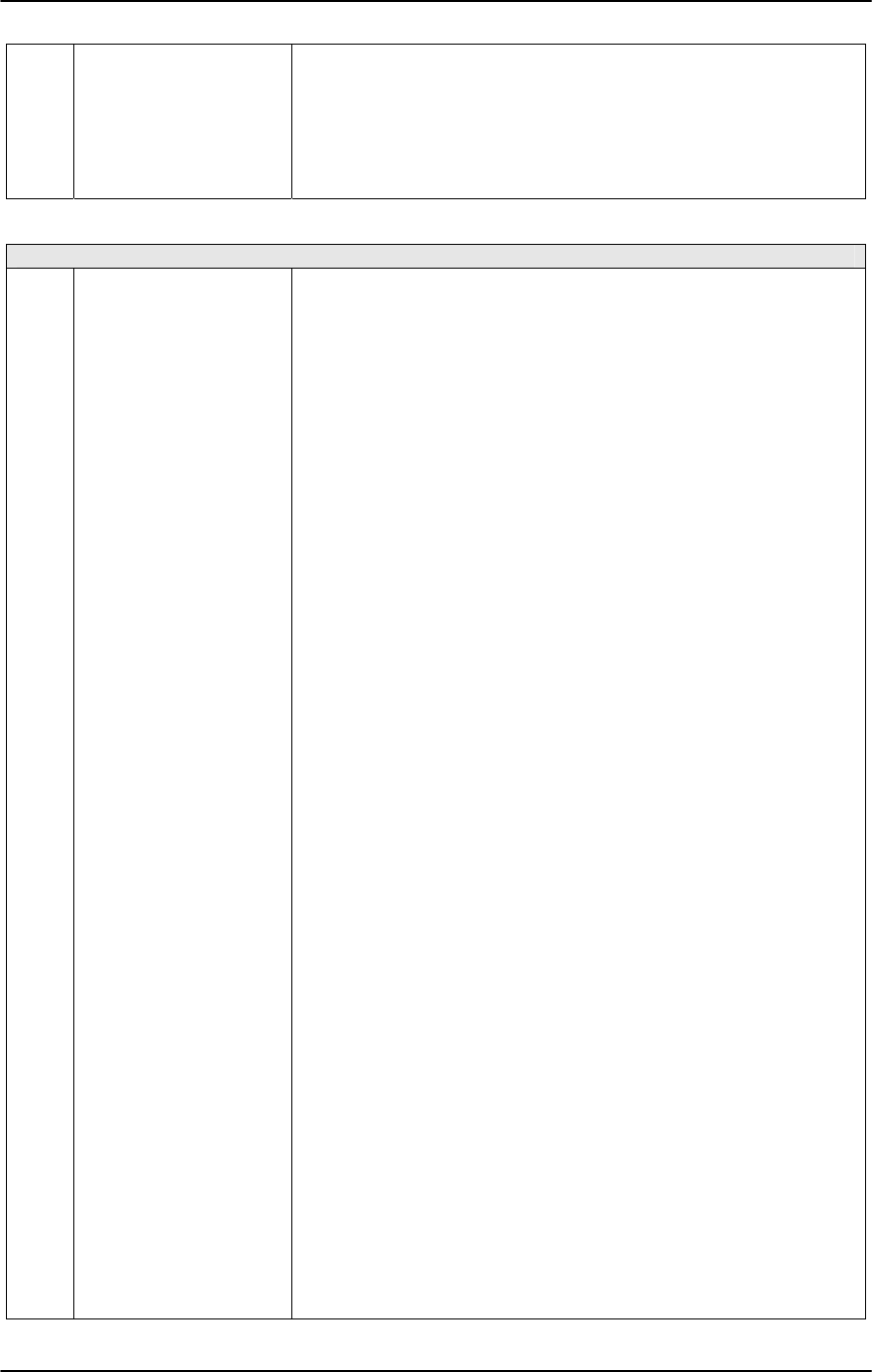

<4>

<77>

Symbol Rate

Reserved

reserved in RCS10/10L mode

Bit 6 = Rx clock fallback. (Not Latched)

Bit 7 = Eb/No Threshold Fault. (Not Latched)

Binary value, 1 sps steps

Reserved

Opcode: <2406h> Query a demodulator’s latched alarms

Query Response

<1>

<1>

<1>

<1>

<1>

<1>

Latched Alarm 1

Latched Alarm 2

Latched Alarm 3

Latched Common

Alarm 1

Latched Common

Alarm 2

Latched Alarm 4

Bit 0 = Receive processor fault Alarm. 1 = Fail

Bit 1 = Carrier Loss 1 = Fail

Bit 2 = Multiframe Sync Loss 1 = Fail

Bit 3 = Frame Sync Loss 1 = Fail

Bit 4 = IBS BER Alarm 1 = Fail

Bit 5 = Satellite AIS 1 = Fail

Bit 6 = Rx Data Activity. 1 = Fail

Bit 7 = Rx AGC Level (Not Latched).

Bit 0 = Buffer underflow. 1 = Fail

Bit 1 = Buffer overflow. 1 = Fail

Bit 2 = Buffer under 10%. 1 = Fail

Bit 3 = Buffer over 90%. 1 = Fail

Bit 4 = RS Decoder Lock Fault. 1 = Fail

Bit 5 = RS De-Interleaver Fault. 1 = Fail

Bit 6 = RS Decoder Uncorrectable Word. 1 = Fail

Bit 7 = Summary Fault. 1 = Fail

Bit 0 = IF synthesizer lock detect Fault. 1 = Fail

Bit 1 = Rx Oversample PLL lock detect. 1 = Fail

Bit 2 = Buffer clock PLL lock detect. 1 = Fail

Bit 3 = Viterbi decoder lock (Not Latched)

Bit 4 = Sequential decoder lock (Not Latched)

Bit 5 = Rx 2047 test pattern lock (Not Latched)

Bit 6 = External reference PLL lock (Not Latched)

Bit 7 = IDR 96 PLL Lock. 1 = Fail

Bit 0 = -12V alarm. 1 = Fail

Bit 1 = +12V alarm. 1 = Fail

Bit 2 = +5V alarm. 1 = Fail

Bit 3 = Reserved

Bit 4 = Battery. 1 = Fail

Bit 5 = RAM and ROM alarm flag. 1 = Fail

Bits 6 and 7 = Spares

Bit 0 = M&C processor fault 1 = Fail

Bit 1 = U IO card present alarm 1 = Fail, reserved in

RCS10/10L mode

Bit 2 = IF card present alarm 1 = Fail

Bits 3 - 7 = Spares

Bit 0 = Buffer clock activity detect. (Not Latched)

Bit 1 = External BNC activity detect. (Not Latched), reserved in

RCS10/10L mode

Bit 2 = Rx satellite clock activity detect. 1 = Fail

Bit 3 = Insert clock activity detect. 1 = Fail

Bit 4 = External reference PLL activity. (Not La

tched), reserved