Rev.1.10 Jul 01, 2005 page 89 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 11. DMAC

Under development

This document is under development and its contents are subject to change.

11.2 DMA Transfer Cycles

Any combination of even or odd transfer read and write addresses is possible.

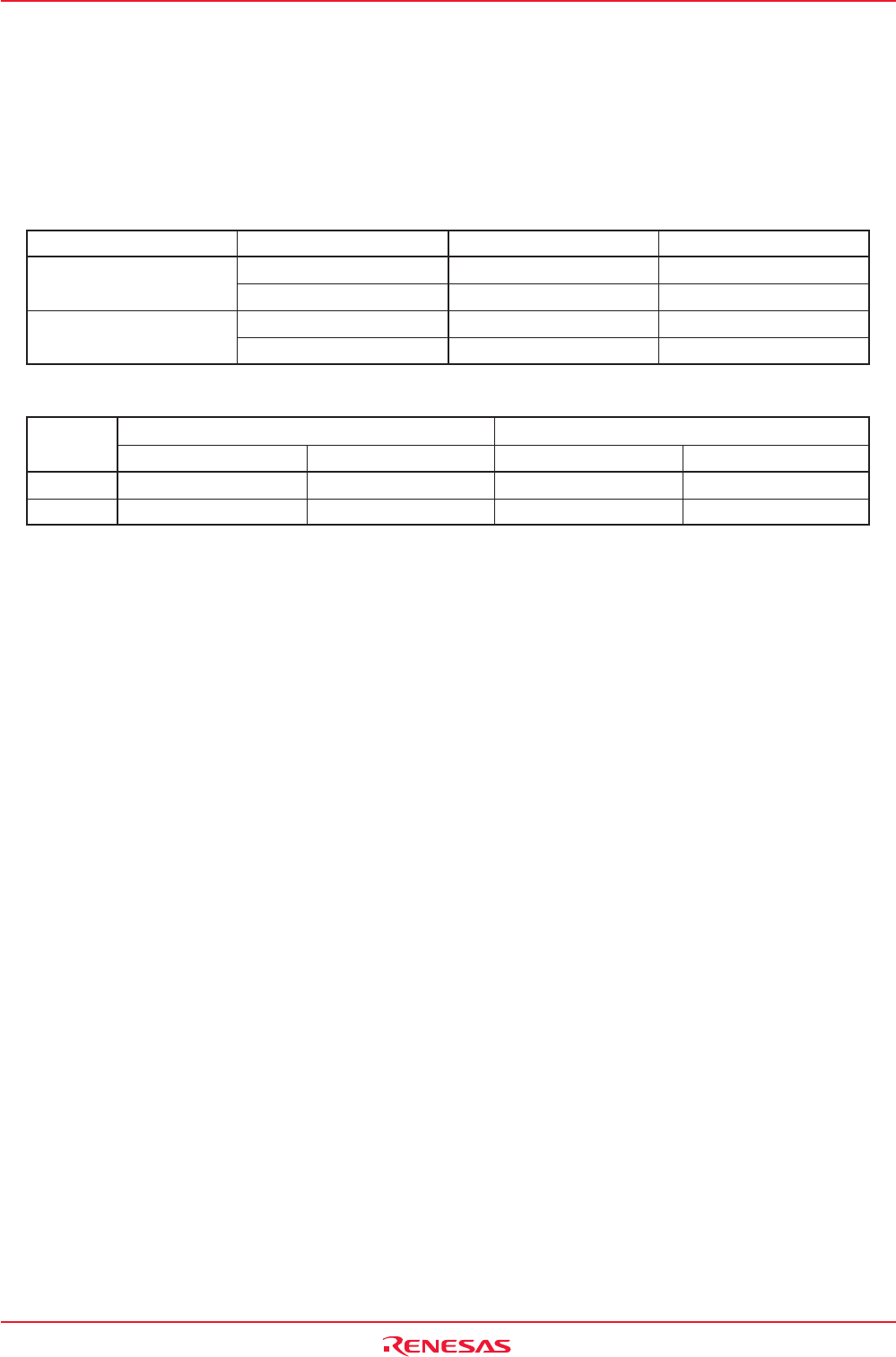

Table 11.2 shows the number of DMA transfer cycles. Table 11.3 shows the coefficient j, k.

The number of DMAC transfer cycles can be calculated as follows:

No. of transfer cycles per transfer unit = No. of read cycles ✕ j + No. of write cycles ✕ k

Table 11.2 DMA Transfer Cycles

Table 11.3 Coefficient j, k

Transfer Unit Access Address No. of Read Cycles No. of Write Cycles

8-bit Transfer Even 1 1

(DMBIT =1) Odd 1 1

16-bit Transfer Even 1 1

(DMBIT = 0) Odd 2 2

NOTE:

1. Depends on the set value of the PM20 bit in the PM2 register.

Internal ROM, RAM SFR

No Wait With Wait 1 Wait

(1)

2 Waits

(1)

j1223

k1223