Rev.1.10 Jul 01, 2005 page 69 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 9. Interrupt

Under development

This document is under development and its contents are subject to change.

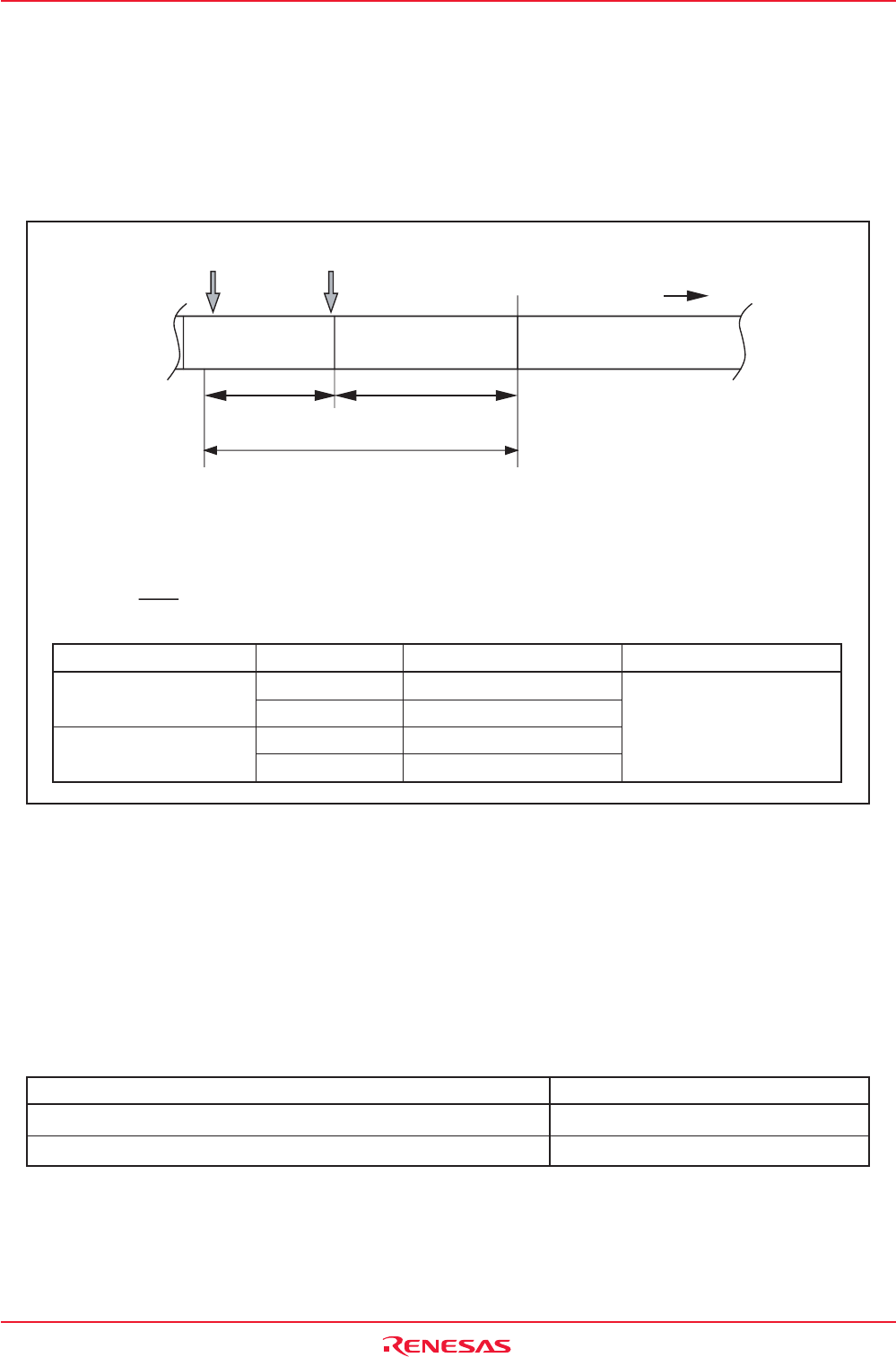

Figure 9.6 Interrupt response time

9.5.6 Variation of IPL when Interrupt Request is Accepted

When a maskable interrupt request is accepted, the interrupt priority level of the accepted interrupt is set

in the IPL.

When a software interrupt or special interrupt request is accepted, one of the interrupt priority levels listed

in Table 9.5 is set in the IPL. Table 9.5 shows the IPL values of software and special interrupts when they

are accepted.

Table 9.5 IPL Level that is Set to IPL When A Software or Special Interrupt is Accepted

9.5.5 Interrupt Response Time

Figure 9.6 shows the interrupt response time. The interrupt response or interrupt acknowledge time

denotes a time from when an interrupt request is generated till when the first instruction in the interrupt

routine is executed. Specifically, it consists of a time from when an interrupt request is generated till when

the instruction then executing is completed ((a) on Figure 9.6) and a time during which the interrupt

sequence is executed ((b) on Figure 9.6).

Interrupt Sources Value that is Set to IPL

_______

Oscillation Stop and Re-oscillation Detection, Watchdog Timer, NMI

_________

Software, Address Match, DBC, Single-Step

Interrupt Vector Address SP Value 16-bit Bus, without Wait 8-bit Bus, without Wait

Even

Odd

Even

Odd

Even

Odd

18 cycles

19 cycles

19 cycles

20 cycles

20 cycles

Instruction Interrupt sequence

Instruction in

interrupt routine

Time

Interrupt response time

(a) (b)

Interrupt request acknowledgedInterrupt request generated

(a) A time from when an interrupt request is generated till when the instruction then

executing is completed. The length of this time varies with the instruction being

executed. The DIVX instruction requires the longest time, which is equal to 30 cycles

(without wait state, the divisor being a register).

(b) A time during which the interrupt sequence is executed. For details, see the table

below. Note, however, that the values in this table must be increased 2 cycles for the

DBC interrupt and 1 cycle for the address match and single-step interrupts.

7

Not changed