Rev.1.10 Jul 01, 2005 page 303 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 22. Usage Precaution

Under development

This document is under development and its contents are subject to change.

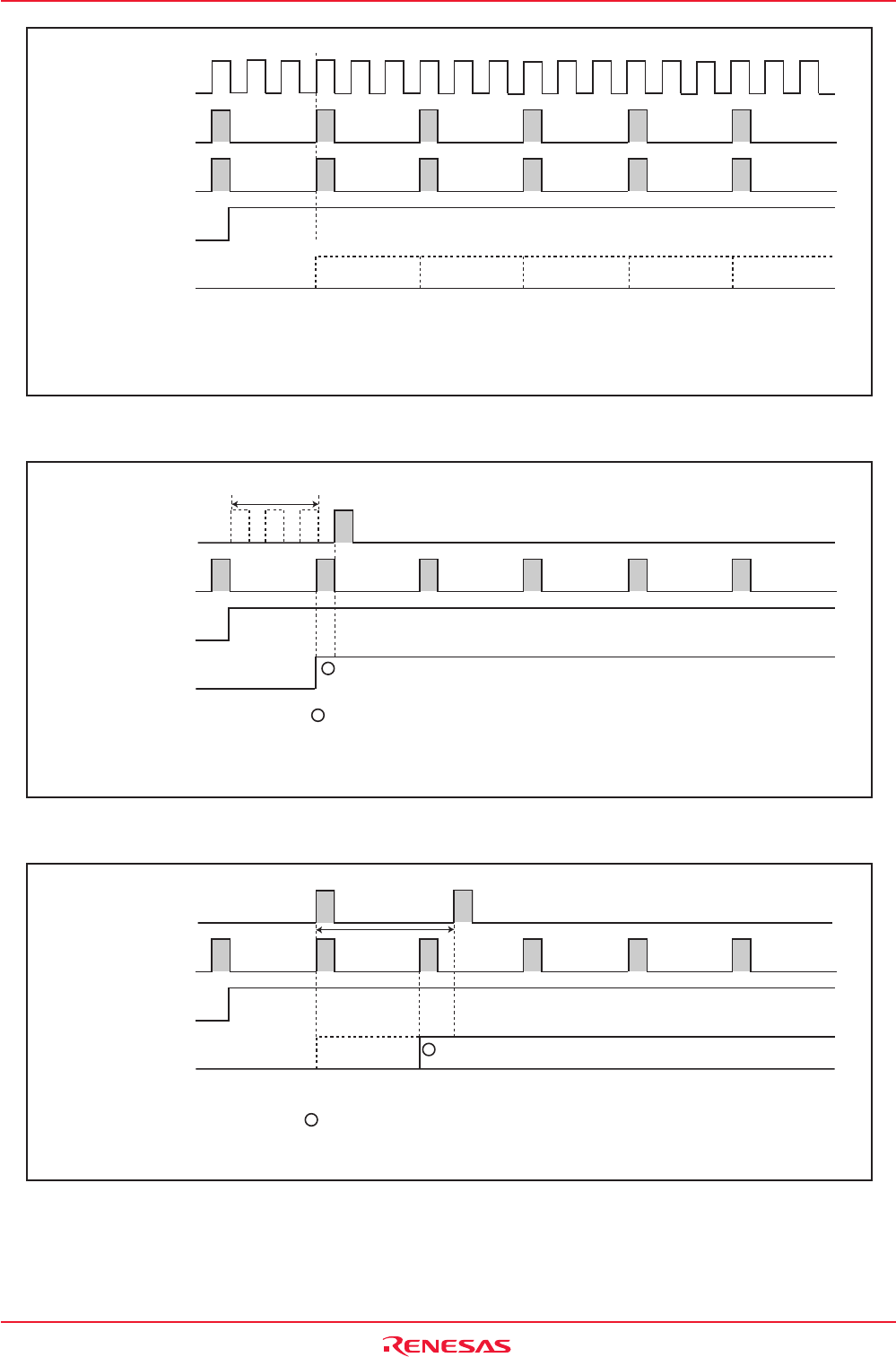

Figure 22.5 When Updating Period of CAN Module Matches Access Period from CPU

fCAN

✕✕✕ ✕✕

CPU read signal

CPU reset signal

Updating period of

CAN module

CiSTR register

b8: State_Reset bit

i = 0, 1

0: CAN operation

mode

1: CAN reset/initial-

ization mode

✕: When the CAN module’s State_Reset bit updating period matches the CPU’s read

period, it does not enter reset mode, for the CPU read has the higher priority.

Figure 22.6 With a Wait Time of 3fCAN Before CPU Read

Figure 22.7 When Polling Period of CPU is 3fCAN or Longer

: Updated without fail in period of 3fCAN

CPU read signal

CPU reset signal

Updating period of

the CAN module

CiSTR register

b8: Reset state flag

Wait time

i = 0, 1

0: CAN operation

mode

1: CAN reset/initial-

ization mode

: Updated without fail in period of 4fCAN

CPU read signal

CPU reset signal

Updating period of

the CAN module

CiSTR register

b8: State_Reset bit

✕

4fCAN

i = 0, 1

0: CAN operation

mode

1: CAN reset/initial-

ization mode

✕: When the CAN module’s State_Reset bit updating period matches the CPU’s read

period, it does not enter reset mode, for the CPU read has the higher priority.