Rev.1.10 Jul 01, 2005 page 100 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 12. Timers

Under development

This document is under development and its contents are subject to change.

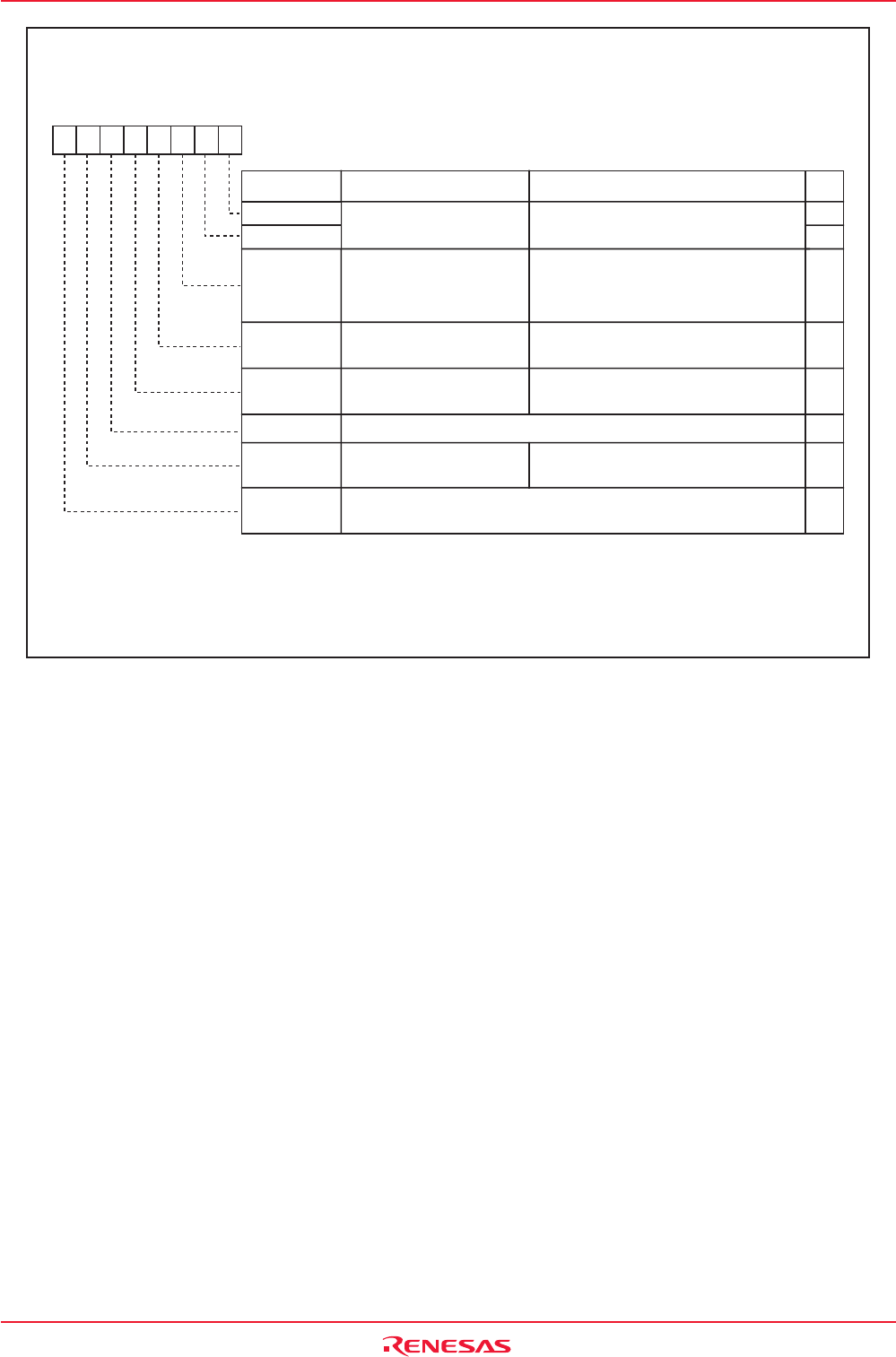

Figure 12.8 TA0MR to TA4MR Registers in Event Counter Mode (when not using two-phase pulse

signal processing)

Symbol Address After Reset

TA0MR to TA4MR 0396h to 039Ah 00h

b7 b6 b5 b4 b3 b2 b1 b0

Operation Mode Select Bit

0 1 : Event counter mode

(1)

b1 b0

TMOD0

MR0

Pulse Output Function

Select Bit

0 : Pulse is not output

(TAiOUT pin functions as I/O port)

1 : Pulse is output

(TAiOUT pin functions as pulse output pin)

Count Polarity Select Bit

(2)

MR2

MR1

MR3

Set to "0" in event counter mode

TCK0

Count Operation Type

Select Bit

010

0 : Counts falling edge of external signal

1 : Counts rising edge of external signal

Up/Down Switching

Cause Select Bit

0 : UDF register

1 : Input signal to TAiOUT pin

(3)

0 : Reload type

1 : Free-run type

Bit Symbol Bit Name Function

RW

TCK1

Can be "0" or "1" when not using two-phase pulse signal processing.

TMOD1

Timer Ai Mode Register (i = 0 to 4)

(When not using two-phase pulse signal processing)

RW

RW

RW

RW

RW

RW

RW

RW

NOTES:

1.During event counter mode, the count source can be selected using the ONSF and TRGSR registers.

2.Effective when the TAiTGH and TAiTGL bits in the ONSF or TRGSR register are "00b" (TAiIN pin input).

3.Count down when input on TAiOUT pin is low or count up when input on that pin is high. The port direction

bit for TAiOUT pin is set to "0" (input mode).