Si5351A/B/C

6 Preliminary Rev. 0.95

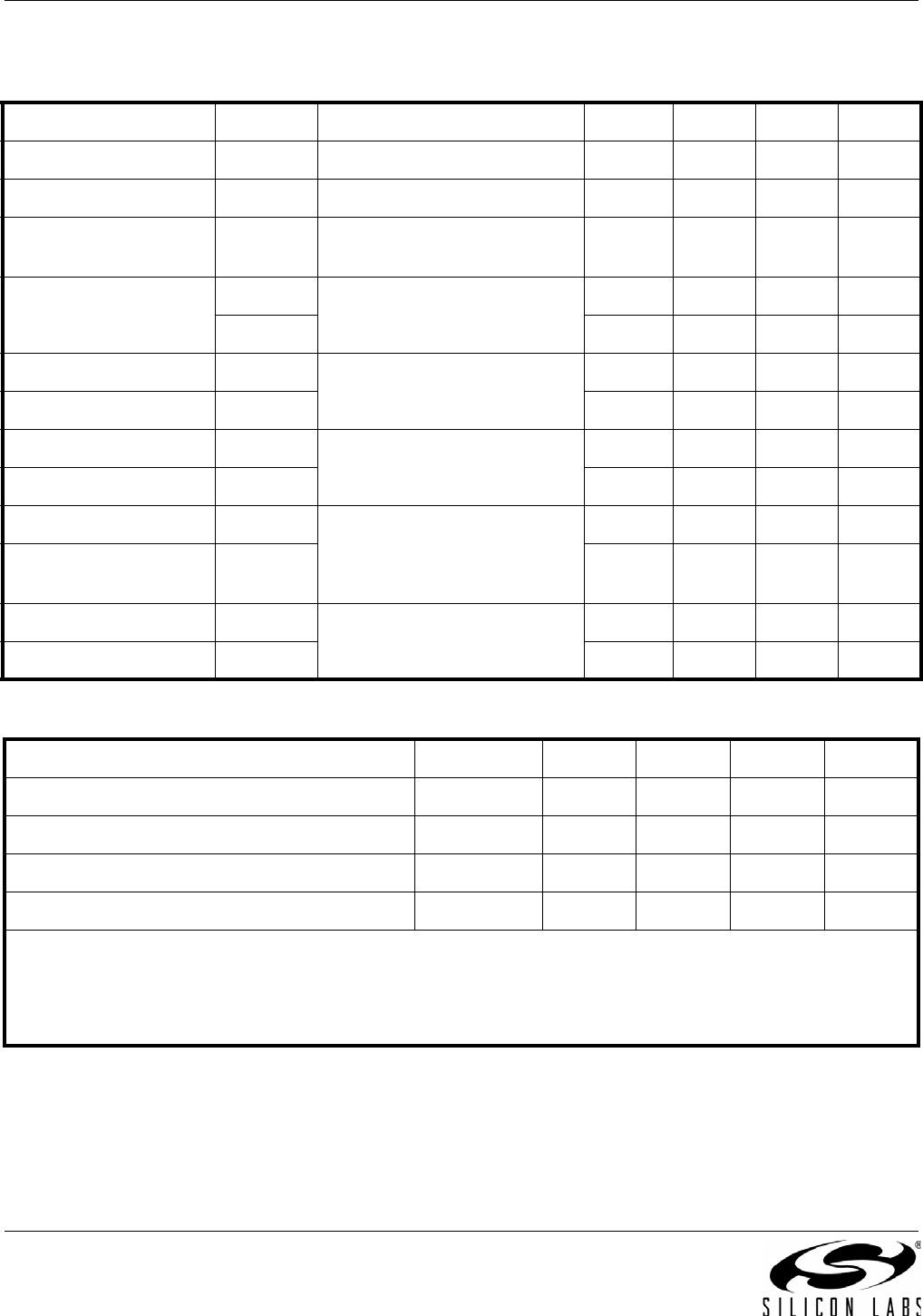

Table 5. Output Clock Characteristics

(V

DD

= 2.5 V ±10%, or 3.3 V ±10%, T

A

=–40 to 85°C)

Parameter Symbol Test Condition Min Typ Max Units

Frequency Range F

CLK

0.008 — 160 MHz

Load Capacitance C

L

—515pF

Duty Cycle DC

Measured at V

DD

/2,

f

CLK

=50MHz

45 50 55 %

Rise/Fall Time

t

r

20%–80%, C

L

=5pF,

Drive Strength = 8 mA

0.5 1 1.5 ns

t

f

0.5 1 1.5 ns

Output High Voltage V

OH

C

L

=5pF

V

DD

– 0.6 — — V

Output Low Voltage V

OL

——0.6V

Period Jitter J

PER

Measured over 10k cycles

— 35 100 ps pk-pk

Period Jitter VCXO J

PER_VCXO

— 60 110 ps pk-pk

Cycle-to-Cycle Jitter J

CC

Measured over 10k cycles

—3090ps pk

Cycle-to-Cycle Jitter

VCXO

J

CC_VCXO

—5095ps pk

RMS Phase Jitter J

RMS

12 kHz–20 MHz

— 3.5 11 ps rms

RMS Phase Jitter VCXO J

RMS_VCXO

— 8.5 18.5 ps rms

Table 6. Crystal Requirements

1,2

Parameter

Symbol Min Typ Max Unit

Crystal Frequency f

XTAL

25 — 27 MHz

Load Capacitance C

L

6—12pF

Equivalent Series Resistance r

ESR

——150

Crystal Max Drive Level d

L

——100µW

Notes:

1. Crystals which require load capacitances of 6, 8, or 10 pF should use the device’s internal load capacitance for

optimum performance. See register 183 bits 7:6. A crystal with a 12 pF load capacitance requirement should use a

combination of the internal 10 pF load capacitors in addition to external 2 pF load capacitors.

2. Refer to “AN551: Crystal Selection Guide” for more details.