TNETX3270

ThunderSWITCH 24/3 ETHERNET SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

34

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

10-/100-Mbit/s MAC interfaces (ports 24–26)

Unlike the 10-Mbit/s ports, each 10-/100-Mbit/s port has a dedicated set of signals to interface to its PHY.

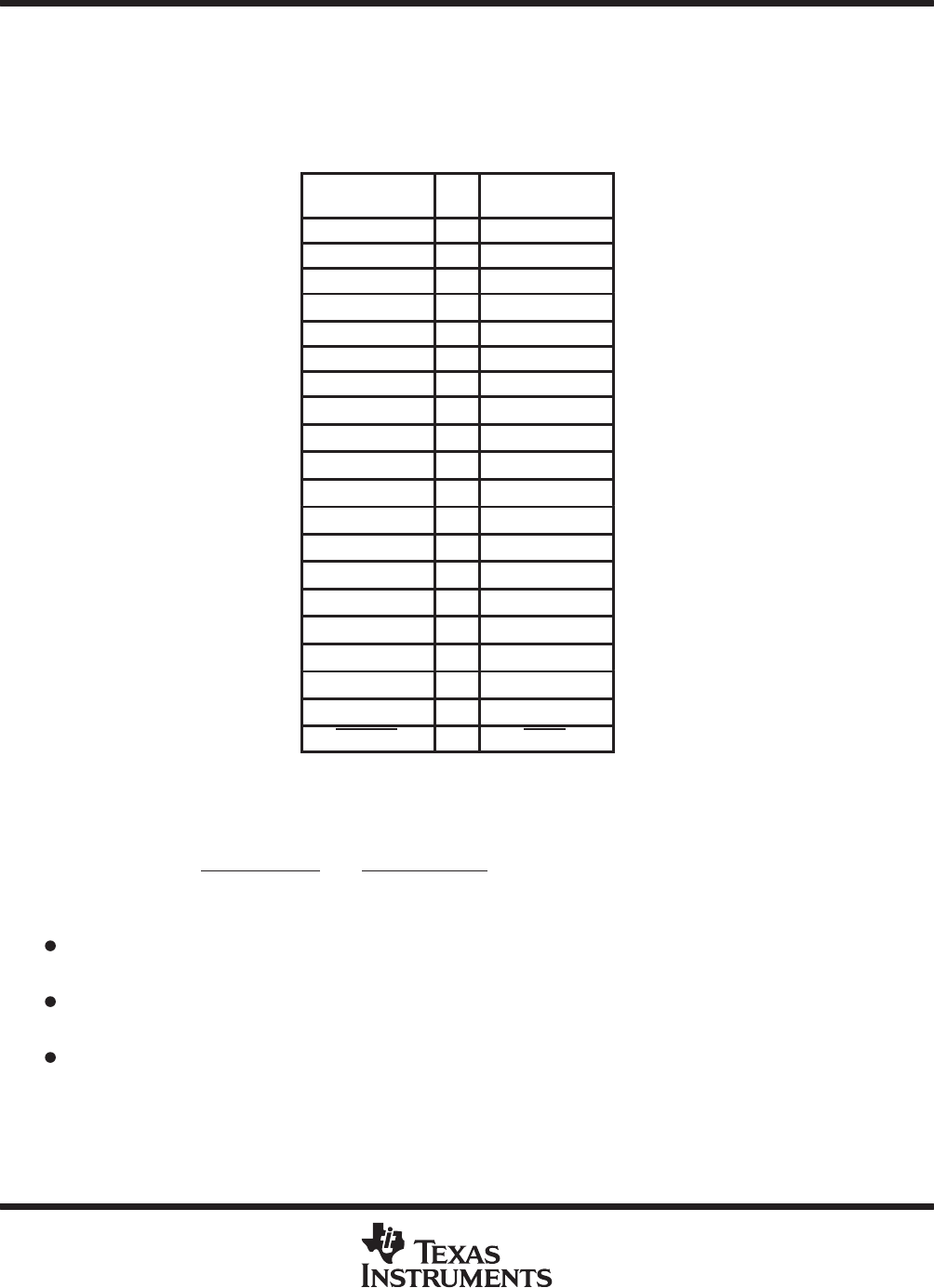

Table 12 shows how a TNETE2101 10-/100-Mbit/s PHY would be connected to one of the 10-/100-Mbit/s ports

of TNETX3270.

Table 12. 10-/100-Mbit/s Interface Connections

SWITCH

TERMINAL

TNETE2101

TERMINAL

MxxTCLK ← MTCLK

MxxTXD3 → MTXD3

MxxTXD2 → MTXD2

MxxTXD1 → MTXD1

MxxTXD0 → MTXD0

MxxTXEN → MTXEN

MxxTXER → MTXER

MxxCOL ← MCOL

MxxCRS ← MCRS

MxxRCLK ← MRCLK

MxxRXD3 ← MRXD3

MxxRXD2 ← MRXD2

MxxRXD1 ← MRXD1

MxxRXD0 ← MRXD0

MxxRXDV ← MRXDV

MxxRXER ← MRXER

MxxLINK ← SLINK

MDCLK → MDCLK

MDIO ↔ MDIO

MRESET → MRST

Where xx = 24, 25, or 26, y = 0–3

Other differences from the 10-Mbit/s ports are noted in following paragraphs.

10-/100-Mbit/s port configuration

The 100-Mbit/s ports (24–26) can negotiate with the PHY (speed and duplex) at power-up via the EEPROM

contents using the MxxFORCE10

and MxxFORCEHD terminals, respectively.

Each of these terminals (per port):

Has an integral 50-µA current-source pullup resistor. The system designer must decide if this is sufficient

to achieve a logic-1 level in a timely manner or if an external supplementary resistor is required.

Has a strong open-drain pulldown transistor, which is enabled by setting to 1 the appropriate bit in the

Portxcontrol register.

Is connected (via synchronization logic) to the appropriate bit in the Portxstatus register. These bits directly

control the configuration of the ports.