TNETX3270

ThunderSWITCH 24/3 ETHERNET SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

35

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

10-/100-Mbit/s port configuration (continued)

Each terminal is considered to be bidirectional, when pulled low by either TNETX3270 or by the PHY (or other

external connections). If neither pulls the terminal low, then the pullup resistor maintains a value of 1 on the

terminal. When the PHY does not pull down a terminal, then it can determine the desired option that is being

requested by TNETX3270. TNETX3270 observes the terminal to determine if its desired option has been

granted.

The sense of these three signals is such that the higher-performance option is represented by a value of 1; if

the MAC does not require the higher performance or the PHY cannot supply it, either can pull the signal low,

forcing the port to use the lower-performance option.

The status of the link for each of these ports is indicated on the MxxLINK terminal and observable in the port’s

Portxstatus register. The MxxLINK terminal plays no part in the negotiation of speed or duplex or their recording

in the Portxstatus register.

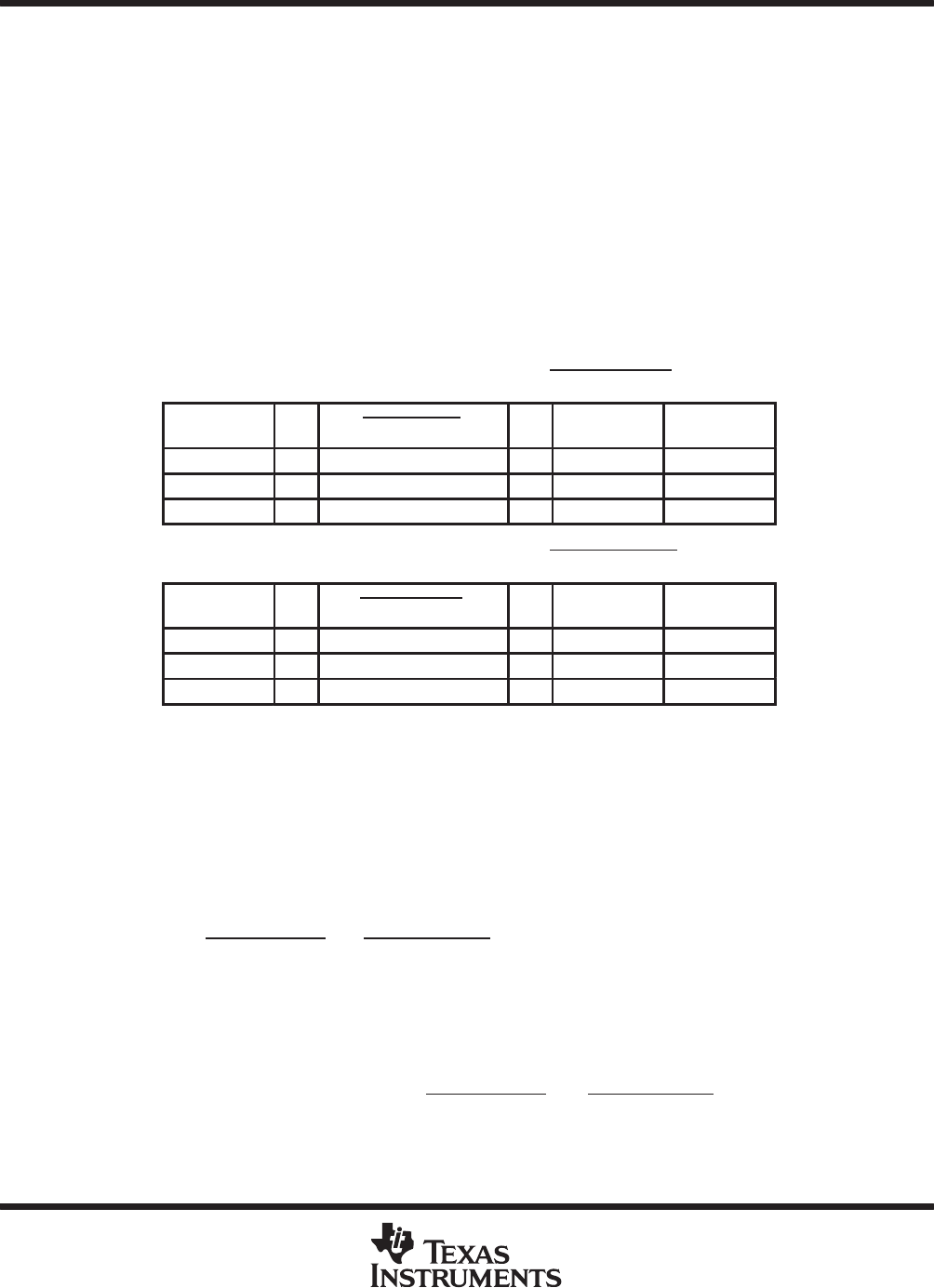

The behavior of these terminals is summarized in Tables 13 and 14.

Table 13. Speed Configuration – MxxFORCE10

Portxcontrol

req10

MxxFORCE10

Portxstatus

SPEED

OUTCOME

(Mbit/s)

0 → Floating 1 → 1 100

1 → Driven 0 (by TNETX3270) → 0 10

X Driven 0 (by PHY) → 0 10

Table 14. Duplex Configuration – MxxFORCEHD

Portxcontrol

reqhd

MxxFORCEHD

Portxstatus

DUPLEX

OUTCOME

0 → Floating 1 → 1 Full duplex

1 → Driven 0 (by TNETX3270) → 0 Half duplex

X Driven 0 (by PHY) → 0 Half duplex

10-/100-Mbit/s port configuration in a nonmanaged switch

The 10-/100-Mbit/s ports can be configured in a nonmanaged switch using the following procedure:

1. The EEPROM loads the req10 and reqhd bits of the Portxcontrol registers as required. If either of these bits

becomes a 1, the corresponding terminal is not pulled low and thus, floats high. (The reqnp bit also can be

loaded from EEPROM to enable/disable pause-frame control in the MAC, but this cannot be communicated

to the PHY. The system designer should ensure that the MAC and PHY operate using the same

pause-frame regime.)

2. The PHYs either:

a. Look at the MxxFORCE10

and MxxFORCEHD terminals and configure themselves as specified (if not

autonegotiating), or as the highest common denominator with the link partner, if they are

autonegotiating. If the PHYs use the information on these terminals, they must wait until TNETX3270

loads the EEPROM contents before doing so (this may require delaying the reset to the PHYs if

necessary).

b. Ignore TNETX3270 requests and configure themselves in some other manner.

3. The PHYs (or external system) then drive MxxFORCE10

and MxxFORCEHD low for those features that

are supported only at the lower performance. These are continuously sampled into the Portxstatus register.

4. The MACs then operate as indicated by the Portxstatus register.