AR-B1375/AR-B1376 User s Guide

7-5

OnBoard FDC

This option enables the floppy drive controller on the AR-B1375 and AR-B1376.

OnBoard Serial Port

This option enables the serial port on the AR-B1375 and AR-B1376.

OnBoard Parallel Port

This option enables the parallel port on the AR-B1375 and AR-B1376.

Parallel Port Mode

This option specifies the parallel port mode. ECP and EPP are both bidirectional data transfer schemes that

adhere to the IEEE P1284 specifications.

Parallel Port DMA Channel

This option is only available if the setting for the parallel Port Mode option is ECP.

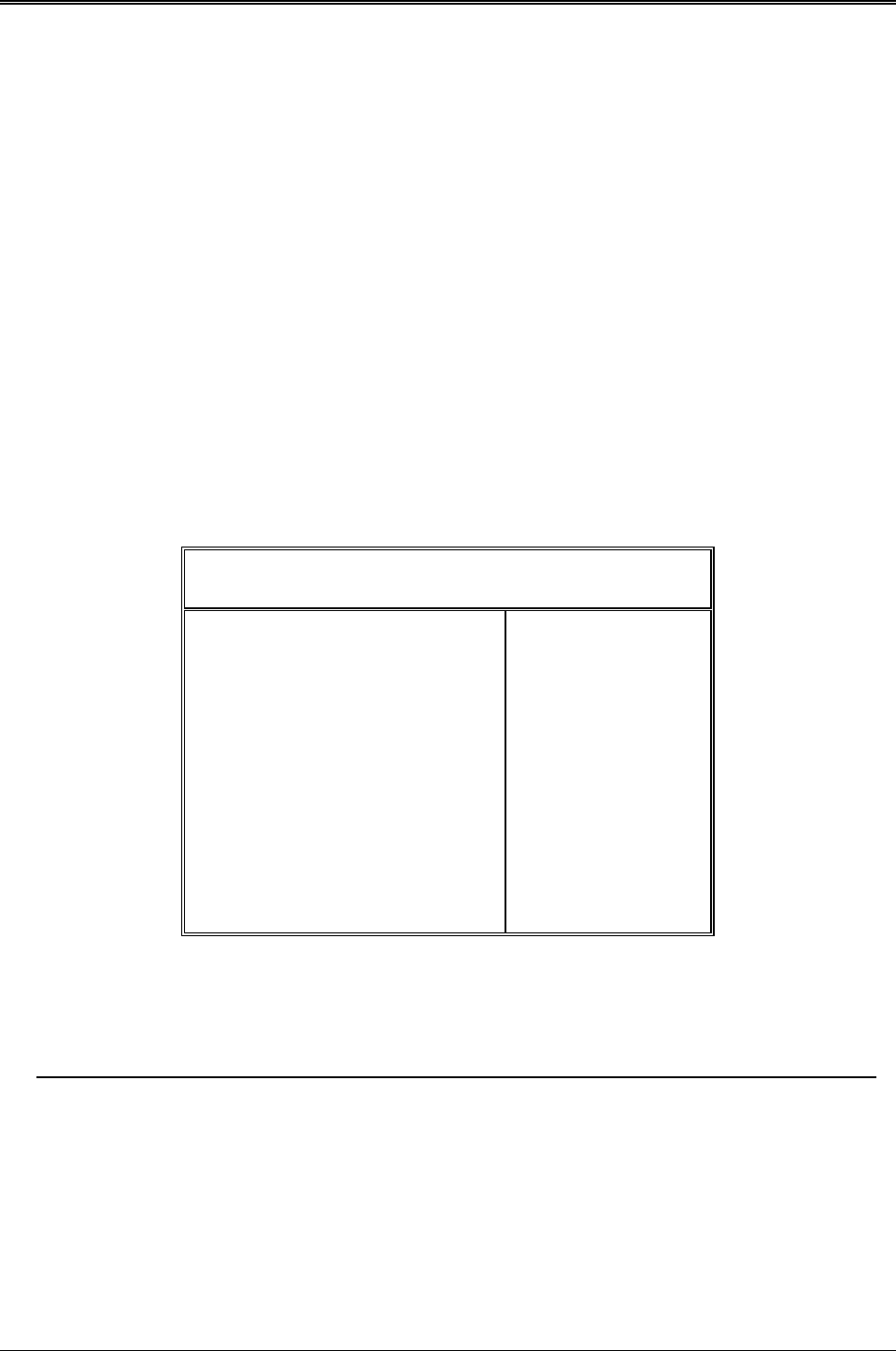

7.4 ADVANCED CHIPSET SETUP

This option controls the configuration of the board’s chipset. Control keys for this screen are the same as for the

previous screen.

AMIBIOS SETUP - ADVANCED CHIPSET SETUP

(C) 1995 American Megatrends, Inc. All Rights Reserved

AT Bus Clock 14.318 / 2

Slow Refresh 60 us

Memory Hole At 15-16M Disable

RAS Precharge time 1.5T

RAS Active Time Insert Wait Disable

CAS Precharge Time Insert Wait Disable

Memory Write Insert Wait Disable

ISA I/O High Speed Disable

ISA Memory High Speed Disable

I/O Recovery Disable

I/O Recovery Period 0 us

16Bit ISA Insert Wait Disable

Available Options :

14. 318/2

PLCK2/3

PLCK2/4

PLCK2/5

PLCK2/6

PLCK2/8

PLCK2/10

PLCK2/12

ESC:Exit ↑↓:Sel

PgUp/PgDn:Modify

F2/F3:Color

Figure 7-4 BIOS: Advanced Chipset Setup

AT Bus Clock

This option sets the polling clock speed of ISA Bus (PC/104).

NOTE:

1. PCLK means the CPU inputs clock.

2. Acrosser recommends user setting at the range of 8MHz to 10MHz.

Slow Refresh

This option sets the DRAM refresh cycle time.

RAS Precharge time

The DRAM RAS precharge time.