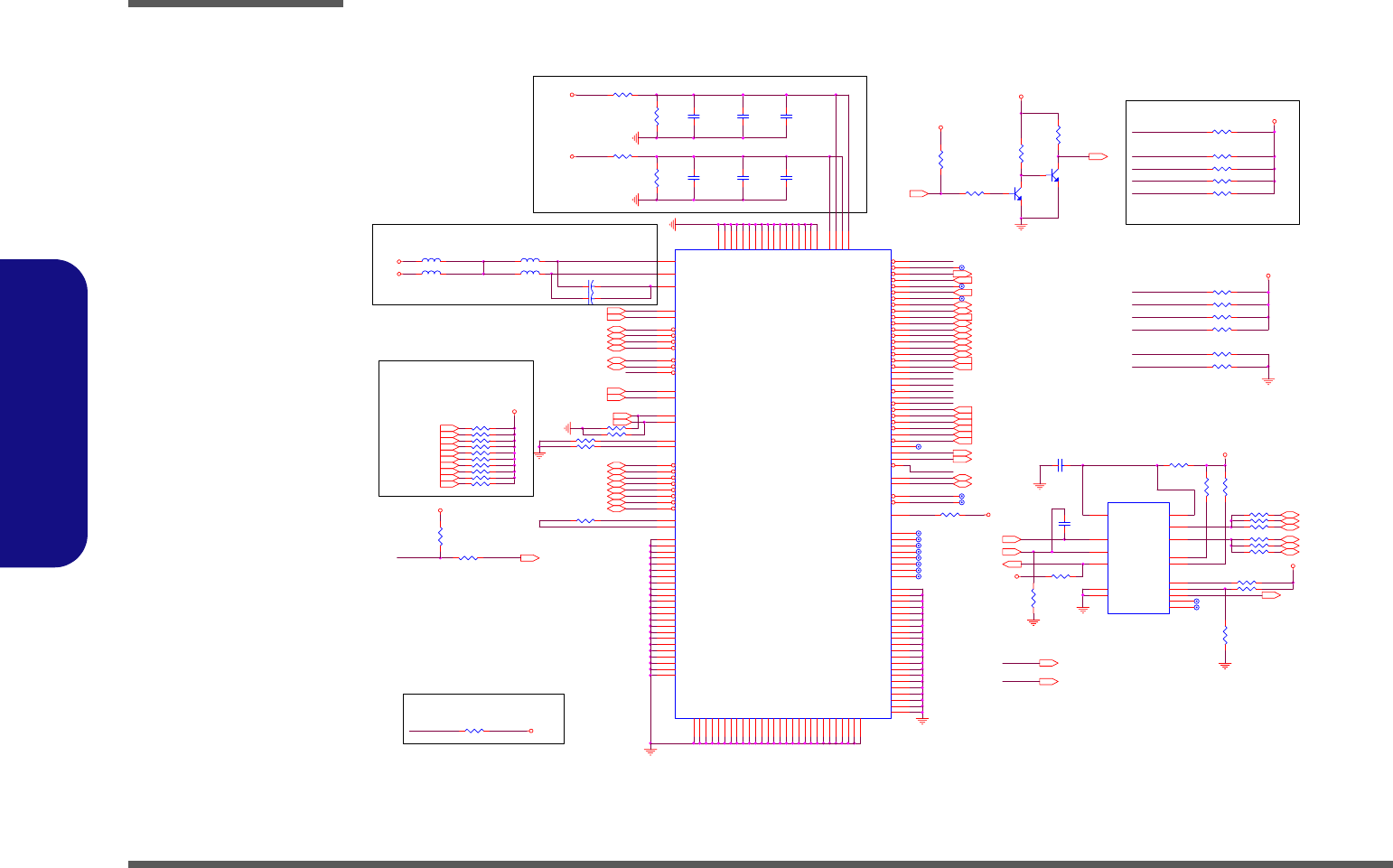

Schematic Diagrams

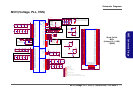

C - 4 CPU (Northwood) 2 of 2 (71-888E0-D04) - For 888E

888E Schematic Diags

CPU (Northwood) 2 of 2

VCORE

VCORE

VCORE

VCORE

VCORE

VCORE

VCORE

1.25V

VCC3S

VCORE

1.25V

VCC3S

VCC3S

VCC3S

VCC3S

IERR#

THERMTRIP#

CPUPWRGD

PROCHOT#

BR0#

TMS

TCK

TDI

TRST#

HCPURST#

NMI

HCPURST#

HLOCK#

BNR#

TDI

PROCHOT#

SMI#

BSEL0

HSTPCLK#

RSP#

ADS#

VCCIOPLL IERR#

HDBI3#

HDBI1#

DBR#

INTR

BR0#

HIT#HDBI0#

COMP_0

BINIT#

HITM#

TMS

THERMDC

INIT#

TDO

IGNNE#

A20M#

COMP_1

MCERR#

HTRDY#

BPRI#

THERMDA

HDBI2#

DEFER#

TCK

TRST#

CPUSLP#

HDRDY#

CPUPWRGD

BSEL1

H_FERR#

DBSY#

THERMTRIP#

TDO

DBR#

VID_VCC

FERR#

TP_DBA_ITP

ATF_INT#

OS#

THERMDA

THERMDC

VSSA

VCCCA

R766 55_1%12

R767 55_1%12

Q23

3904

B

E

C

R290

470

R308

300

Q24

3904

B

E

C

R312

56

R286 470

R287 1_1%

T155

R259 33(R)

R784 0(R)

R783 0

R785 0(R)

R786 0(R)

R787 0(R)

R788 0

L55 L(0805)1 2

L50 L(0805)(R)1 2

C381

220P_X7R

12

C383

220P_X7R

12

C382

1U_0805_X7R

12

R271

100_1%

12

C428

220P_X7R

12

C427

220P_X7R

12

C426

1U_0805_X7R

12

R293

100_1%

12

L51 4.7UH(0805)1 2

R272 51.1_1%12

+

CP7 10U(1206)1 2

+

CP6 10U(1206)1 2

R270 49.9_1%1 2

R292 49.9_1%1 2

R313 10K12

R309 56_1%12

R268 300_1%12

R302 56_1%12

L53

4.7UH(0805)

1 2

R305 51_1%12

R295 27.4_1%12

R300 68012

R344 51_1%12

R304 3912

R296 15012

C448 0.1U

1 2

R284 10K(R)

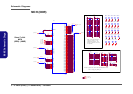

U33

TC1066

15

12

14

6

10

1

5

9

13

16

2

3

4

11

7

8

STBY#

SMBDATA

SMBCLK

ADD1

ADD0

NC/CRIT1

NC/CRIT0

NC/OS#

NC

NC

VCC

DXP

DXN

ALERT#

GND

GND

R321 10K 0805(R)

C444

2200P

R319

4.7K

R320 200

R317

4.7K

R316 8.2K

R289 R12

R298 51.1_1%12

R299 200

R343 200

R301 200

R314

4.7K(R)

R310 200

R311 200

R291 200

R348 200

R297 200

R303 200

R294 200

T162

T161

T150

T158

T152

T148

T151

T156

T159

R759

10K

T149

T153

T147

T146

R329 7512

R347 15012

U34B

NORTHWOOD478

AC1

V5

A5

AC26

AD26

AE25

L5

R5

P1

E5

D1

F6

F20

AA6

AA21

W23

P23

J23

F21

W22

R22

K22

E22

AF23

AF22

AC3

V6

B6

Y4

AA3

W5

AB2

H5

H2

J6

G1

G4

H6

G2

F3

E3

D2

E2

D4

C1

F7

E6

D5

B3

C4

A2

C3

B2

B5

C6

AB26

AB23

AB25

A4

V21

P26

G25

E21

C25

C5

C7

C9

D10

D12

D14

D16

D18

D20

D21

D24

D3

D6

D8

AE23

AD20

AD22

K24

K3

K6

L1

L23

L26

L4

M2

M22

M25

M5

N21

N24

N3

N6

P2

P22

P25

P5

E13

E15

E17

E19

E23

E26

E4

E7

E9

F10

F12

F14

F16

F18

F2

F22

F25

F5

J2

J22

J25

J5

K21

R1

R23

T6

U2

U22

U25

U5

V1

V23

V26

V4

W21

W24

W3

W6

Y2

Y22

Y25

Y5

G6

R26

E11

E1

F8

G21

G24

T3

T24

T21

G3

R4

AD6

AD5

L24

AF4

C22

A22

A7

AD2

AD3

AE21

AF3

AF24

AF25

B1

AP0

AP1

VCC_SENSE

ITP_CLK0

ITP_CLK1

DBRESET

ADSTB0

ADSTB1

COMP1

LINT1

LINT0

GTLREF3

GTLREF2

GTLREF1

GTLREF0

STBP3

STBP2

STBP1

STBP0

STBN3

STBN2

STBN1

STBN0

BCLK1

BCLK0

IERR

MCERR

FERR

STPCLK

BINIT

INIT

RSP

DBSY

DRDY

TRDY

ADS

LOCK

BR0

BNR

HIT

HITM

BPRI

DEFER

TCK

TDI

TMS

TRST

TDO

THERMDA

THERMDC

THERMTRIP

PROCHOT

IGNNE

SMI

A20M

SLP

PWRGOOD

RESET

VSS_SENSE

DB#3

DB#2

DB#1

DB#0

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCCIOPLL

VCCA

VSSA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

BSEL0

BSEL1

COMP0

VCCVID

VSS

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5/VCCVIDPRG

RESERVED6

RESERVED7

NC

T430

T431

R789

0(R)

VCORE [2,4,6,19,42]

PM_CPUPERF#[2,19]

SMI#[18]

IGNNE#[18]

CPUSLP#[18]

A20M#[18]

NMI[18]

INTR[18]

DPSLP#[2,18,42]

INIT#[18]

HSTPCLK#[18]

VCC3 [10,13,17,18,19,21,26,27,28,29,30,31,32,34,35,37,40,42]

SMI# [18]

HIT# [5]

IGNNE# [18]

BR0# [5]

DBSY# [5]

HLOCK# [5]

H_FERR#

BSEL0 [10]

HDRDY# [5]

DEFER# [5]

HITM# [5]

CPUSLP# [18]

INIT# [18]

A20M# [18]

BSEL1 [10]

BPRI# [5]

HSTPCLK# [18]

THERMDA

HCPURST# [5]

ADS# [5]

HTRDY# [5]

CPUPWRGD [19]

THERMDC

HDBI1#[5]

ITPCLK#[10]

BNR# [5]

NMI[18]

HDSTBP0#[5]

HDSTBP2#[5]

HADSTB0#[5]

HDSTBP1#[5]

HADSTB1#[5]

HDSTBN0#[5]

HDBI3#[5]

INTR[18]

HDSTBN3#[5]

HDBI0#[5]

ITPCLK[10]

HDSTBN1#[5]

HDBI2#[5]

HDSTBP3#[5]

HDSTBN2#[5]

FERR# [18]

H_FERR#

AGP_BUSY# [11,19]

CPUCLK#[10]

CPUCLK[10]

THERMDA

THERMDC

ATF_INT#[19,30]

OS# [26]

SMB_ICHCLK [9,10,19,25]

SMB_ICHDATA [9,10,19,25]

SCL_ATF [25,30,43]

SDA_ATF [25,30,43]

SDA_H8 [30]

SCL_H8 [30]

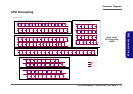

GTLREF GENERATION CIRCUITS

CPU SIGNAL TERMINATION

CLOSE TO CPU

Placement : 3 " form CPU (MAX)

RES Place close to ITP

12mil trace

VCCA route parallel and VSSA route

L should be close to c

Layout Note:

20 mils

20 mils

Sheet 3 of 44

CPU 2 of 2 (888E)