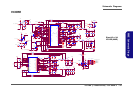

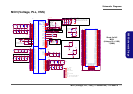

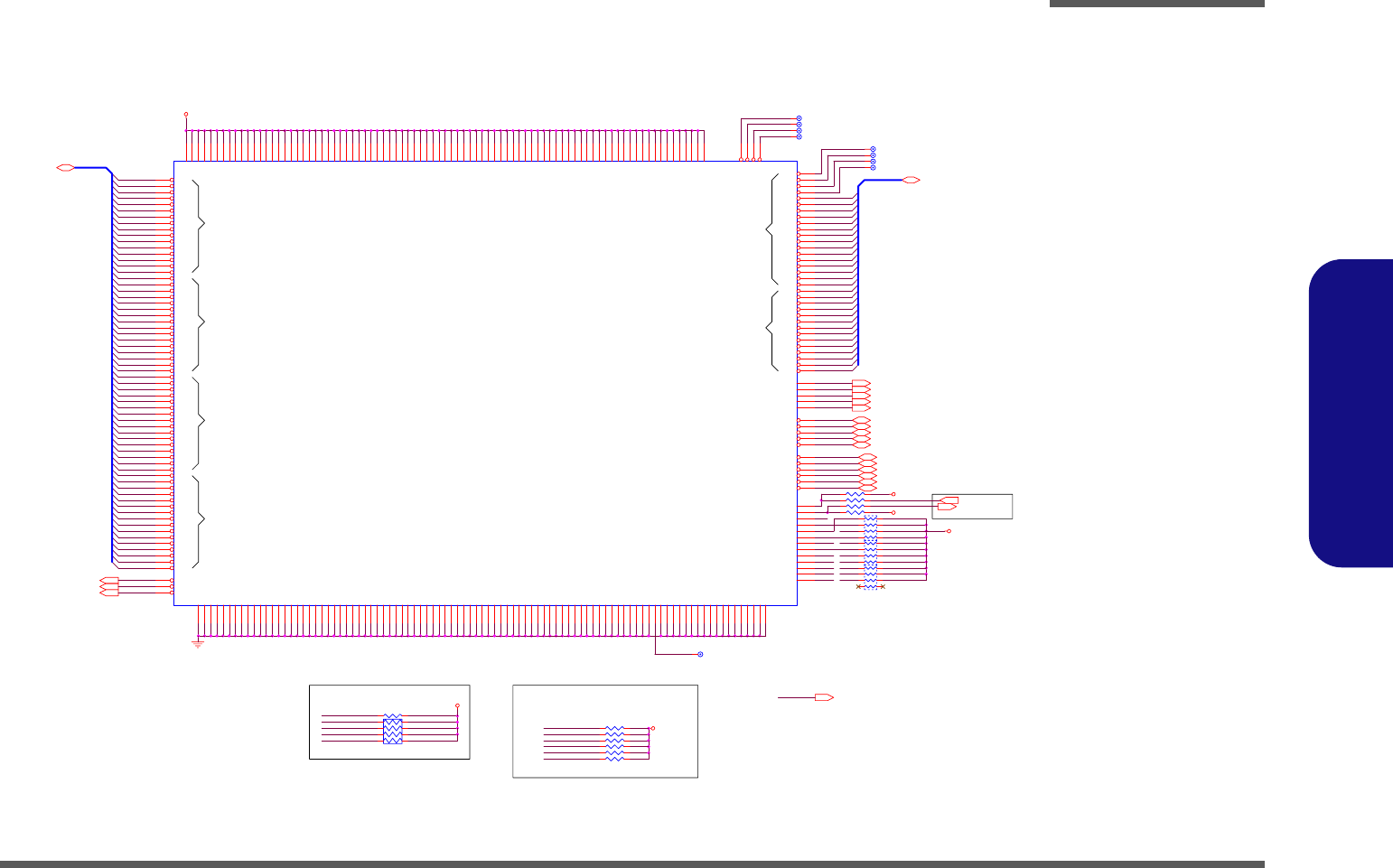

Schematic Diagrams

CPU (Northwood) 1 of 2 (71-88800-D04) - For 8880 D - 3

8880 Schematic Diags

CPU (Northwood) 1 of 2

Sheet 2 of 45

CPU 1 of 2 (888C)

VCC3S

VCORE

VCORE

VCORE

VCORE

VCORE

VID2

VID4

VID1

VID0

VID3

BPM2#

TPREQ#

BPM0#

BPM1#

BPM3#

TPRDY#

HD[0..63]

HD1

HD15

HD19

HD20

HD27

HD35

HD44

HA3

HA5

HREQ0#

HRS1#

HA32

HD7

HD16

HD30

HA12

HA22

VID4

HD11

HD22

HD42

HD55

HA23

HD33

HD41

HD50

HA7

HA18

VID1

HA35

HD26

HD32

HD59

HA27

HD29

HD38

HD40

HA4

HA9

HA10

HA20

HA25

HD36

HA8

HA15

Z123

VID0

HD21

HD58

HD63

HA11

HA24

HREQ3#

VID2

HA33

HA34

HD10

HD28

HD45

HD48

HA26

HREQ4#

HD0

HD12

HD13

HD37

HD47

HA16

HA28

SKTOCC#

HD17

HD34

HD39

HD49

HD54

BPM2#

HD6

HD46

HD62

HA29

HA30

HRS2#

HRS0#

HD3

HREQ1#

Z120

Z125

DP3#

HD5

HD23

HD43

HA6

HA14

HA19

DP1#

HD9

HD25

HD52

HD60

HREQ2#

VID3

HD2

HD4

HD24

HD31

HD53

HD61

HA13

HA17

HA21

HD8

HD14

HD18

HD51

HD56

HD57

DP2#

DP0#

TPREQ#

TPRDY#

BPM3#

BPM1#

BPM0#

HA31

PM_CPUPERF#

DPSLP#

Z124

Z126

Z122

Z121

Z120

Z121

Z124

Z122

Z126

Z123

Z125

RN47

8P4R_10K

1

2

3

4

8

7

6

5

RN48

8P4R_10K

1

2

3

4

8

7

6

5

RN46

8P4R_10K

1

2

3

4

8

7

6

5

R288 10K1 2

R283 51

R282 51

R281 51

R285 51

R315 51

R318 51

RN45

8P4R_10K

1

2

3

4 5

6

7

8

T164

T145

T154

T143

T142

T144

U34A

NORTHWOOD478

B21

B22

A23

A25

C21

D22

B24

C23

C24

B25

G22

H21

C26

D23

J21

D25

H22

E24

G23

F23

F24

E25

F26

D26

L21

G26

H24

M21

L22

J24

K23

H25

M23

N22

P21

M24

N23

M26

N26

N25

R21

P24

R25

R24

T26

T25

T22

T23

U26

U24

U23

V25

U21

V22

V24

W26

Y26

W25

Y23

Y24

Y21

AA25

AA22

AA24

K2

K4

L6

K1

L3

M6

L2

M3

M4

N1

M1

N2

N4

N5

T1

R2

P3

P4

R3

T2

U1

P6

U3

T4

V2

R6

W1

T5

U4

V3

W2

Y1

AB1

AD24

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AC24

AC23

AB22

AC21

F4

G5

F1

U6

W4

Y3

AC20

AA20

J26

K25

K26

L25

AE1

AE2

AE3

AE4

AE5

AA2

A10

A12

A14

A16

A18

A20

A8

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

B7

B9

C10

C12

C14

C16

C18

C20

C8

D11

D13

D15

D17

D19

D7

D9

E10

E12

E14

E16

E18

E20

E8

F11

F13

F15

F17

F19

F9

H1

H4

H23

H26

A11

A13

A15

A17

A19

A21

A24

A26

A3

A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF26

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26

B4

B8

C11

C13

C15

C17

C19

C2

A6

AD25

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

TESTHI0/BYPASSEN#

BPM5

BPM4

BPM3

BPM2

BPM1

BPM0

REQ4

REQ3

REQ2

REQ1

REQ0

TESTHI4/MCLK2

TESTHI5/MCLK3

TESTHI7/MCLKIO1

TESTHI2/MCLK0

RS2

RS1

RS0

TESTHI8/BR3#

TESTHI9/BR2#

TESTHI10/BR1#

TESTHI3/MCLK1

TESTHI6/MCLKIO0

DEP0

DEP1

DEP2

DEP3

VID4

VID3

VID2

VID1

VID0

TESTHI1/ODT

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKTOCC#

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

TESTHI11/GHI#

TESTHI12/DPSLP#

R307 10K1 2

R338 0(R)1 2

R306 0(R)1 2

R332 10K1 2

T160

T157

T163

VCORE 3,4,6,21,43

HD[0..63]5

VID0 38

VID4 38

VID2 38

HREQ0# 5

HREQ2# 5

HREQ4# 5

HREQ1# 5

VID3 38

VID1 38

HREQ3# 5

BPM0# 3

BPM1# 3

BPM2#

BPM3#

TPRDY# 3

TPREQ# 3

HRS0#5

HRS1#5

HRS2#5

HA[3..31] 5

DPSLP# 3,20,43

PM_CPUPERF# 3,21

Reserved

Place close to cpu

LAYOUT NOTICE:

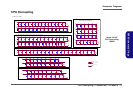

HD[0..15]»Ýµ¥ªø, »~®t

+/-100mils.

¥B©MHDSTBN0#, HDSTBP0#, HDBI0#

µ¥ªø, »~®t+/-25mils.

LAYOUT NOTICE:

HD[16..31]»Ýµ¥ªø, »~®t

+/-100mils.

¥B©MHDSTBN1#, HDSTBP1#, HDBI1#

µ¥ªø, »~®t+/-25mils.

LAYOUT NOTICE:

HD[32..47]»Ýµ¥ªø, »~®t

+/-100mils.

¥B©MHDSTBN2#, HDSTBP2#, HDBI2#

µ¥ªø, »~®t+/-25mils.

LAYOUT NOTICE:

HD[48..63]»Ýµ¥ªø, »~®t

+/-100mils.

¥B©MHDSTBN3#, HDSTBP3#, HDBI3#

µ¥ªø, »~®t+/-25mils.

LAYOUT NOTICE:

HD[0..63]

Data Line lengths:

2"-10" from pin to

pin.

LAYOUT NOTICE:

HA[3..31]

Address Line lengths:

2"-10" from pin to

pin.

LAYOUT NOTICE:

HA[3..16]»Ýµ¥ªø,

»~®t+/-200mils.

¥B©MADSTB0#, HREQ[0..4]#µ¥ªø,

»~®t+/-25mils.

LAYOUT NOTICE:

HA[17..35]»Ýµ¥ªø,

»~®t+/-200mils.

¥B©MADSTB1#µ¥ªø,

»~®t+/-25mils.

Line to line spacing: Greater than

3:1

Trace Impedance: 50ohm +/-15%

For Mobile Northwood

Processor