PMC-CGM Installation and Use (6806800D53C)

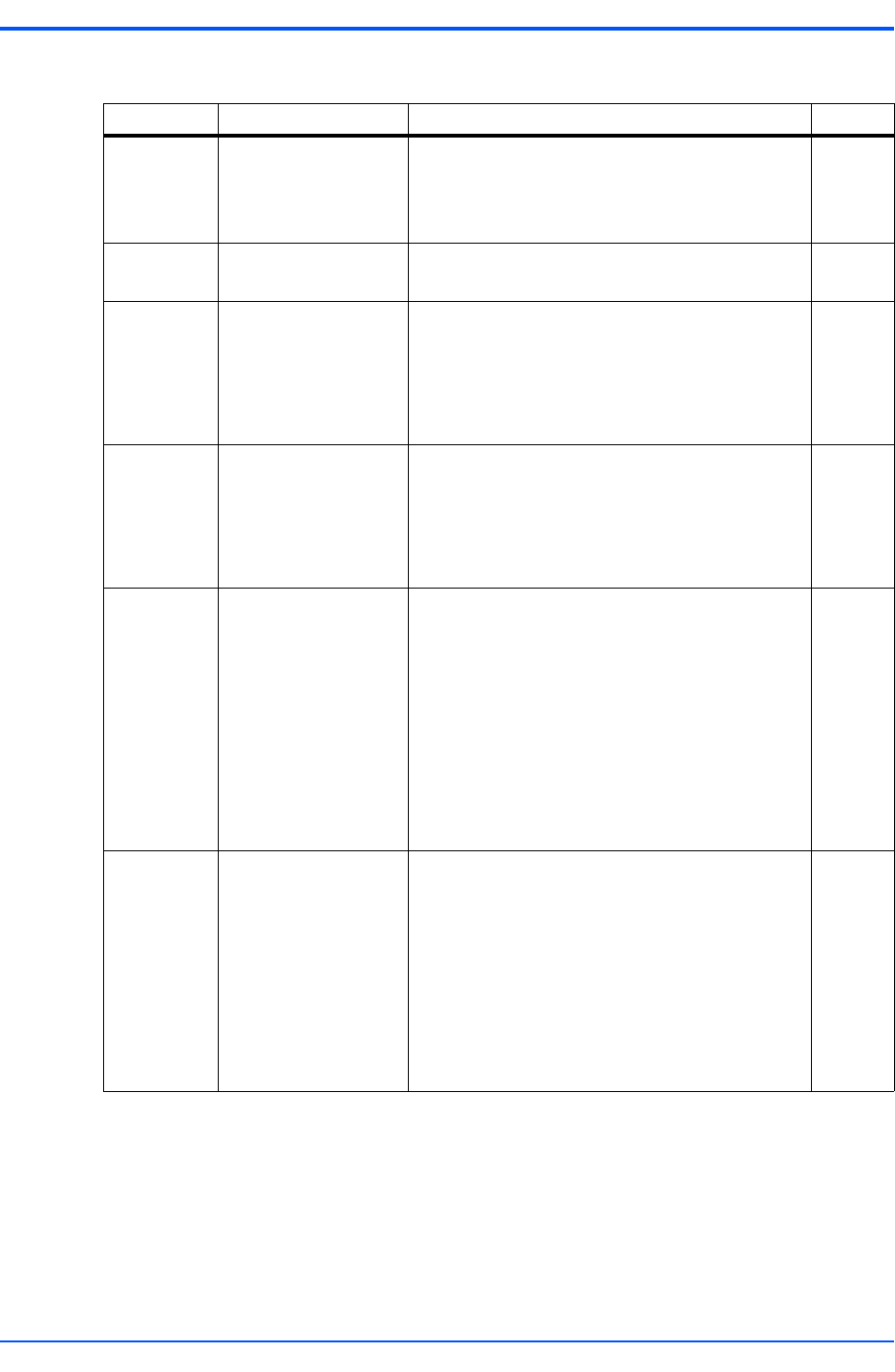

MIB Description cgmControl

52

.1.1.2.1.81 bitsT1TraiCi Transmit RAI-CI

Setting this bit causes the ESF RAI-CI code to be

transmitted in the FDL bit position.

Default value is (0).

r/w

.1.1.2.1.91 bitsE1RxSyncC Frame resynchronization criteria

Default value is (0).

r/w

.1.1.2.1.112 bitsT3ClkForce When set to (1), it, forces the T3 clock output from

the framer to be output to the PLL even if no signal

is present. This should only be set for test purposes

since the framer will generate a free-running clock

in the absence of a valid input.

Default value is (0).

r/w

.1.1.2.1.113 bitsT3ClkSquelch When set to disabled (1), it forces the T3 output to

the PLL to be active even if a loss of frame or an

alarm condition exists. This would typically be

disabled for normal operation and only be set for

unframed operation.

Default value is (0).

r/w

.1.1.2.1.114 bitsTestPattern An 8- or 16-bit test pattern that will be serialized and

repeatedly output on T1E1 port when the test

output is enabled.

Applies to the following line-type settings:

dsx1ESF

dsx1D4

dsx1E1

dsx1E1CRCMF

dsx1E1unframed

Default value is (0).

r/w

.1.1.2.1.115 bitsTestPatternLength Determines whether a 8 bit (0) or 16 bit (1) test

pattern is generated.

Applies to the following line-type settings:

dsx1ESF

dsx1D4

dsx1E1

dsx1E1CRCMF

dsx1E1unframed

Default value is (0).

r/w

Table 5-4 cgmBitsTable (continued)

OID MIB Object Description Access