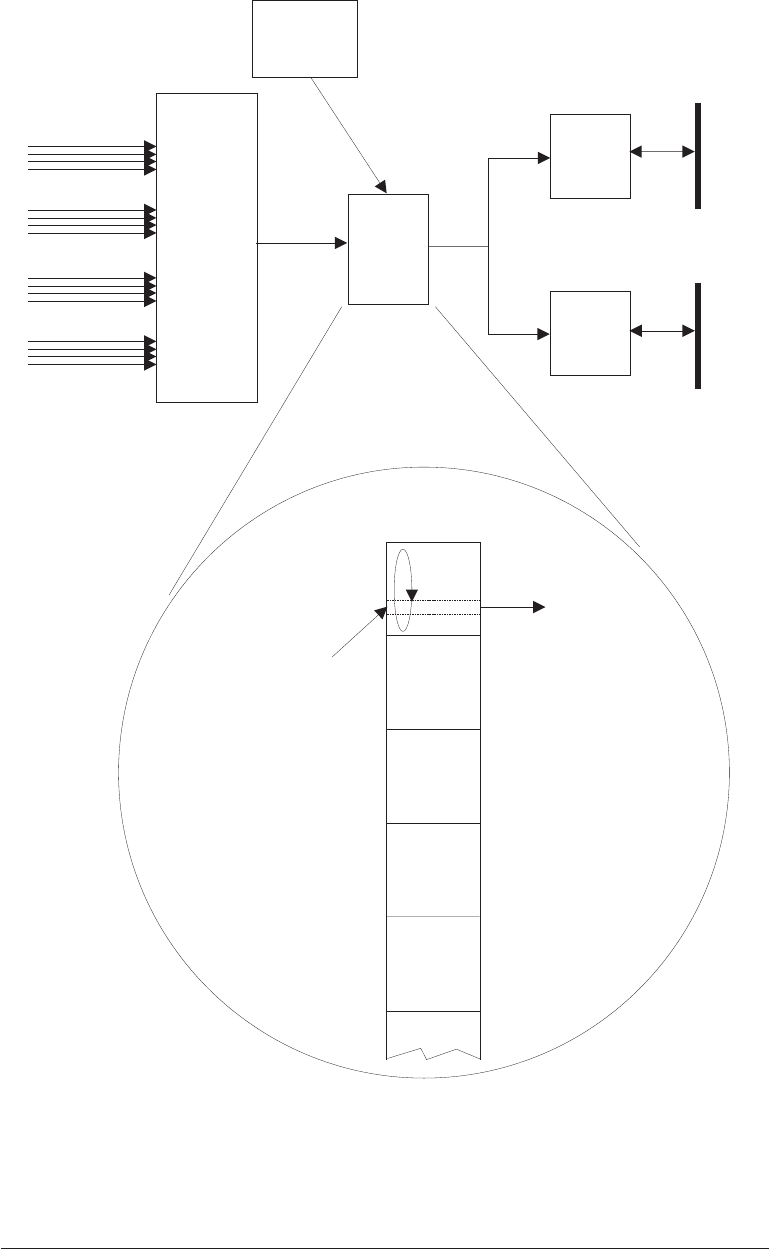

Input 1

Input 3

Input 2

Input 4

Static

RAM

FIFO

FIFO

96002

96002

trigger

Local

host

Bus

port

VME Bus

Local Bus

FIFO

ch 1

ch 3

ch 2

ch 4

ch 5

(DRAM)

trigger

circular

buffer

Bus

Bus

to VME

or Local

........

ch 1

ch 16

Figure 3-11: Data flow and FIFO architecture

HP E1432A User's Guide

Using the HP E1432A

3-16