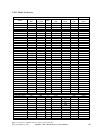

1650016500

248 MB500840-2420 (1547)

1000016500

248 MB500840-2420 (1546)

455016500

248 MB500840-2420 (1545)

200016500

248 MB500840-2420 (1544)

105016500

248 MB500840-2420 (1543)

56016500

248 MB500840-2420 (1542)

24016500

248 MB500840-2420 (1541)

12016500

248 MB500840-2420 (1540)

1000010000

128 MB500840-2418 (1546)

455010000

128 MB500840-2418 (1545)

200010000

128 MB500840-2418 (1544)

105010000

128 MB500840-2418 (1543)

56010000

128 MB500840-2418 (1542)

24010000

128 MB500840-2418 (1541)

12010000

128 MB500840-2418 (1540)

45507350

84 MB540830-2403 (1537)

20007350

84 MB540

830-2403 (1536)

10507350

84 MB540830-2403 (1535)

5607350

84 MB540830-2403 (1534)

2407350

84 MB540830-2403 (1533)

1207350

84 MB540830-2403 (1532)

707350

84 MB540830-2403 (1531)

20004200

44 MB540830-2402 (1536)

10504200

44 MB540830-2402 (1535)

5604200

44 MB540830-2402 (1534)

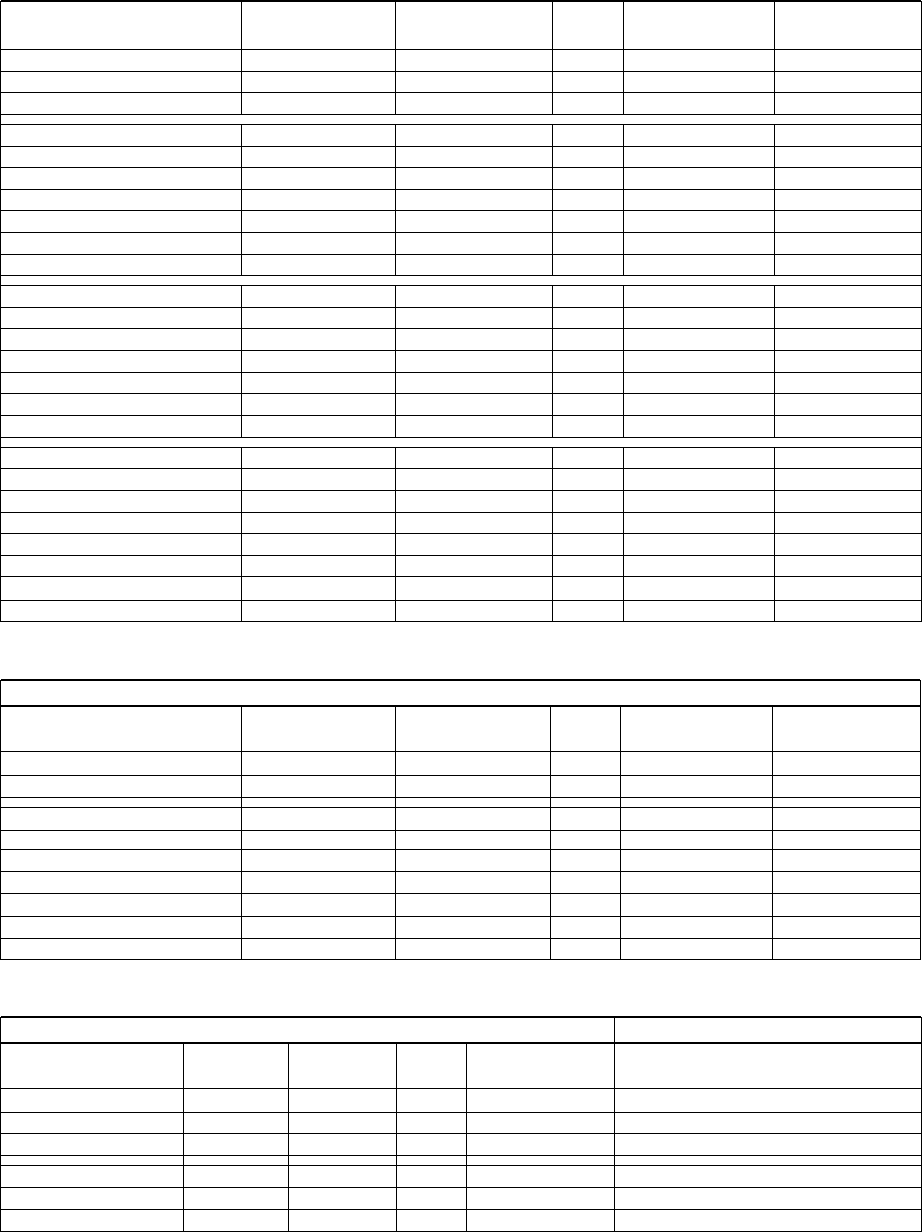

Interactive CPWProcessor CPW

CPUs

L2 cache

per CPU

Chip Speed

MHz

Model

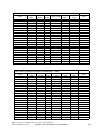

C.11.2 Model 2xx Servers

702000

24 MB450270-2253

(

1520

)

02000

24 MB450270-2253 (1516)

50950

1

2 MB

450270-2252 (1519)

0950

12 MB450270-2252 (1516)

30370

1n/a400270-2250 (1518)

0370

1n/a400270-2250

(

1516

)

25150

1n/a400270-2248 (1517)

2075

1n/a200 250-2296

1550

1n/a200250-2295

Interactive CPWProcessor CPW

CPUs

L2 cache

per CPU

Chip Speed

MHz

Model

Table C.11.2.1 Model 2xx Servers

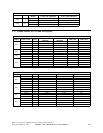

C.11.3 Dedicated Server for Domino

0200

24 MB450270-2424

0100

12 MB450270-2423

050

1n/a400270-2422

0300

44 MB500820-2427

0200

24 MB500820-2426

0100

12 MB450820-2425

Interactive CPW

Non Domino

CPW

CPUs

L2 cache

per CPU

Chip Speed

MHz

Model

Table C.11.3.1 Dedicated Server for Domino

IBM i 6.1 Performance Capabilities Reference - January/April/October 2008

© Copyright IBM Corp. 2008 Appendix C CPW, CIW and MCU for System i Platform 360