Intel

®

Compute Module MFS2600KI TPS Functional Architecture

Revision 1.0 11

Intel order number: G51989-002

Table 3. Intel

®

Compute Module MFS2600KI PCIe Bus Segment Characteristics

CPU#

Device

Physical Connector

Electrical

Width

CPU1

Intel

®

C602-J

N/A

x4 Gen2

CPU1

IO Mezzanine Card

120 pin

Mezzanine Card

Connector

x8 Gen2

CPU1

Intel

®

I350 NIC

N/A

x4 Gen2

CPU1

LSI* 1064e SAS

N/A

x8 Gen1

3.3.2 DMI2 Interface to the PCH

The platform requires an interface to the legacy Southbridge (PCH) which provides basic,

legacy functions required for the server platform and operating systems. Since only one PCH is

required and allowed for the system, CPU2 which does not connect to PCH would use this port

as a standard x4 PCI Express 2.0 interface.

3.3.3 Integrated IOAPIC

Provides support for PCI Express devices implementing legacy interrupt messages without

interrupt sharing.

3.3.4 Intel

®

QuickData Technology

Used for efficient, high bandwidth data movement between two locations in memory or from

memory to I/O.

3.4 Memory Subsystem

3.4.1 Integrated Memory Controller (IMC) and Memory Subsystem

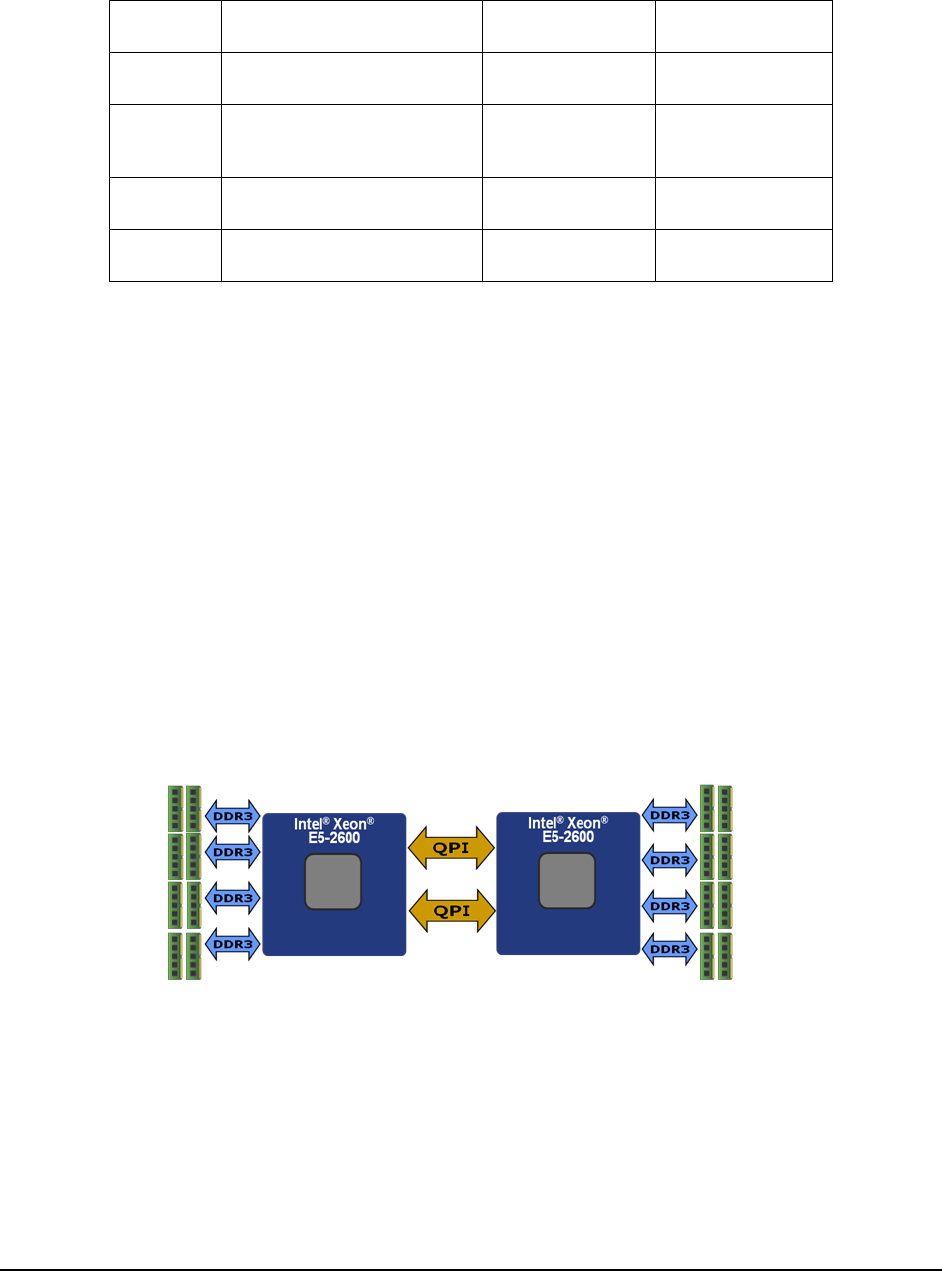

Figure 5. Intergrated Memory Controller (IMC) and Memory Subsystem

Integrated into the processor is a memory controller. Each processor provides four DDR3

channels that support the following:

Unbuffered DDR3 and registered DDR3 DIMMs

LR DIMM (Load Reduced DIMM) for buffered memory solutions demanding higher

capacity memory subsystems

CPU 2

CPU 1

2 DIMMs/Ch

2 DIMMs/Ch