Connector/Header Locations and Pin-outs Intel

®

Compute Module MFS2600KI TPS

Revision 1.0

Intel order number: G51989-002

34

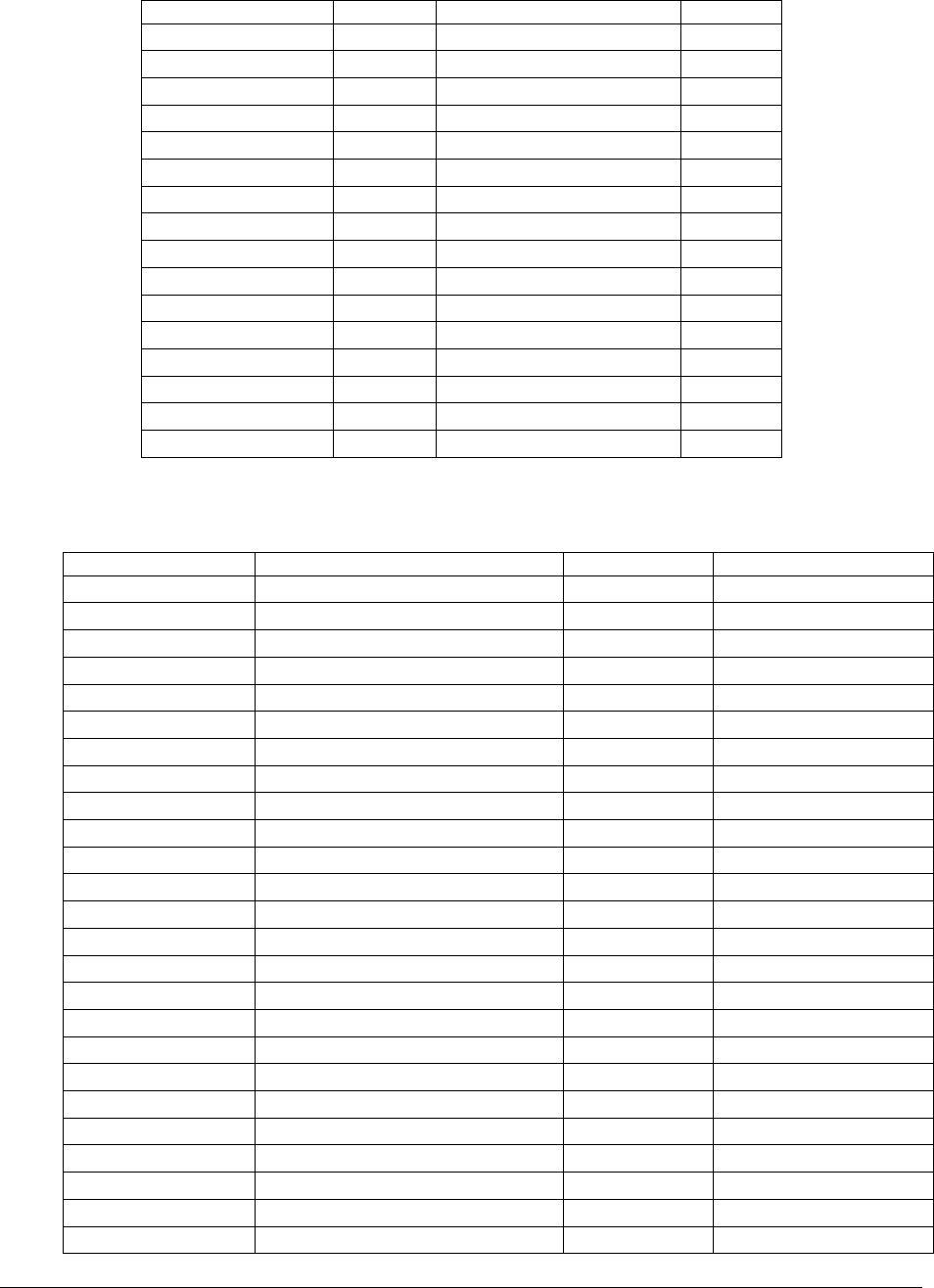

Signal Name

Pin

Signal Name

Pin

GND

89

PCIe_1_D_TXP

90

GND

91

PCIe_1_D_TXN

92

PCIe_1_D_RXP

93

GND

94

PCIe_1_D_RXN

95

GND

96

GND

97

Mezz_Present

98

GND

99

Reset_N

100

Clk0_100M_PCIE_P

101

GND

102

Clk0_100M_PCIE_N

103

GND

104

GND

105

Rsvd

106

GND

107

Rsvd

108

Rsvd

109

GND

110

Rsvd

111

Rsvd

112

Rsvd

113

Rsvd

114

P12V

115

P12V

116

P12V

117

P12V

118

P12V

119

P12V

120

Table 19. 120-pin I/O Mezzanine Card Connector Signal Definitions

Signal Name

Signal Description

Purpose

Connector Location

PCIe_0_A_TXP

PCIe TX+ of Lane A Link 0

Host connect

34

PCIe_0_A_TXN

PCIe TX- of Lane A Link 0

Host connect

36

PCIe_0_A_RXP

PCIe RX+ of Lane A Link 0

Host connect

37

PCIe_0_A_RXN

PCIe RX- of Lane A Link 0

Host connect

39

PCIe_0_B_TXP

PCIe TX+ of Lane B Link 0

Host connect

42

PCIe_0_B_TXN

PCIe TX- of Lane B Link 0

Host connect

44

PCIe_0_B_RXP

PCIe RX+ of Lane B Link 0

Host connect

45

PCIe_0_B_RXN

PCIe RX- of Lane B Link 0

Host connect

47

PCIe_0_C_TXP

PCIe TX+ of Lane C Link 0

Host connect

50

PCIe_0_C_TXN

PCIe TX- of Lane C Link 0

Host connect

52

PCIe_0_C_RXP

PCIe RX+ of Lane C Link 0

Host connect

53

PCIe_0_C_RXN

PCIe RX- of Lane C Link 0

Host connect

55

PCIe_0_D_TXP

PCIe TX+ of Lane D Link 0

Host connect

58

PCIe_0_D_TXN

PCIe TX- of Lane D Link 0

Host connect

60

PCIe_0_D_RXP

PCIe RX+ of Lane D Link 0

Host connect

61

PCIe_0_D_RXN

PCIe RX- of Lane D Link 0

Host connect

63

PCIe_1_A_TXP

PCIe TX+ of Lane A Link 1

Host connect

66

PCIe_1_A_TXN

PCIe TX- of Lane A Link 1

Host connect

68

PCIe_1_A_RXP

PCIe RX+ of Lane A Link 1

Host connect

69

PCIe_1_A_RXN

PCIe RX- of Lane A Link 1

Host connect

71

PCIe_1_B_TXP

PCIe TX+ of Lane B Link 1

Host connect

74

PCIe_1_B_TXN

PCIe TX- of Lane B Link 1

Host connect

76

PCIe_1_B_RXP

PCIe RX+ of Lane B Link 1

Host connect

78

PCIe_1_B_RXN

PCIe RX- of Lane B Link 1

Host connect

79

PCIe_1_C_TXP

PCIe TX+ of Lane C Link 1

Host connect

82