SE7221BK1-E Technical Product Specification

Revision 1.3

10

interfaces that can be independently configured to operate in PCI (33 or 66 MHz), PCI-X

Mode1 (66,100,133), for either 32 or 64 bits.

4.1.1 GMCH Memory Architecture Overview

The GMCH supports a 72-bit wide memory sub-system that can support a maximum of 4 GB of

DDR2 memory using 1 GB DIMMs. This configuration needs external registers for buffering the

memory address and control signals. The four chip selects are registered inside the GMCH and

need no external registers for chip selects.

The memory interface runs at 400/533MT/s. The memory interface supports a 72-bit wide

memory array. It uses seventeen address lines (BA [2:0] and MA [13:0]) and supports 256 Mb,

512 Mb, 1 Gb DRAM densities. The DDR DIMM interface supports memory scrubbing, single-bit

error correction, and multiple bit error detection and Intel® x4 SDDC with x4 DIMMs.

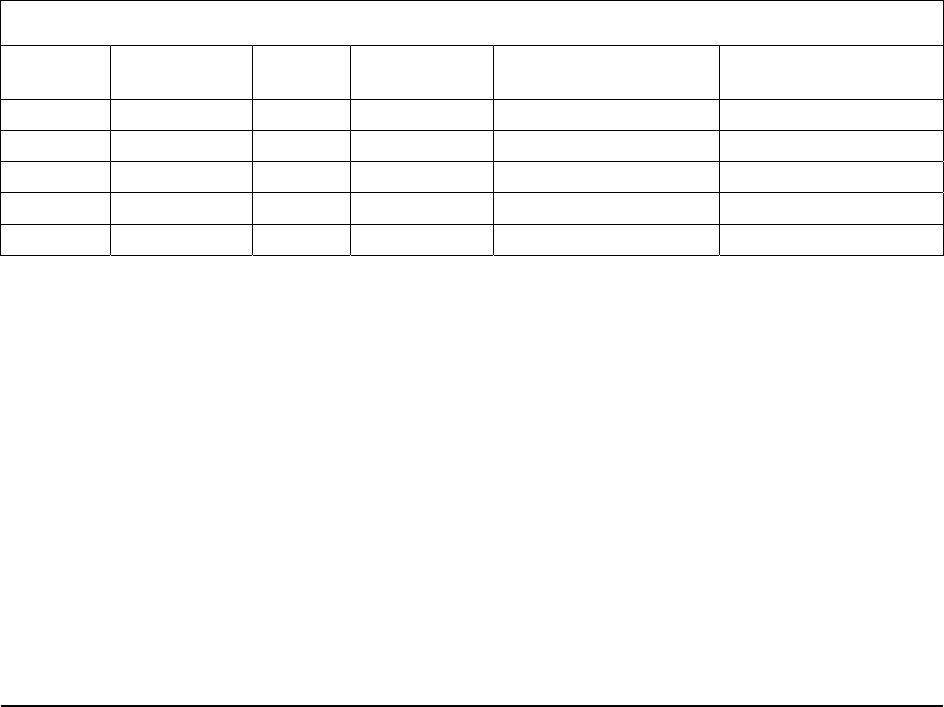

4.1.1.1 DDR2 Configurations

The DDR2 interface supports up to 4 GB of main memory and supports single- and double-

density DIMMs. The DDR2 can be any industry-standard DDR2. The following table shows the

DDR2 DIMM technology supported.

Table 4. Supported DDR2 modules

DDR2-400 and DDR2-533 Un-buffered

SDRAM Module Matrix

DIMM

Capacity

DIMM

Organization

SDRAM

Density

SDRAM

Organization

# SDRAM

Devices/rows/Banks

# Address bits

rows/Banks/column

256MB 32M x 72 256Mbit 32M x 8 9 /1 / 4 13 / 2 / 10

512MB 64M x 72 256Mbit 32M x 8 18 / 2 / 4 13 / 2 / 10

512MB 64M x 72 512Mbit 64M x 8 9 / 1 / 4 14 / 2 / 10

1GB 128M x 72 512Mbit 64M x 8 18 / 2 / 4 14 / 2 / 10

1GB 128M x 72 1Gbit 128M x 8 9 / 1 / 8 14 / 3 / 10

4.1.2 Graphics Memory Controller Hub (GMCH)

The GMCH is a 1210-ball FC-BGA device and uses the proven components of previous

generations like the Intel® Pentium® 4 processor bus interface unit, the hub interface unit, and

the DDR2 memory interface unit. In addition, the GMCH incorporates an integrated high

performance graphics media accelerator and a PCI Express* interface. The PCI Express*

interface allows the GMCH to directly interface with the PCI Express* devices (like PXH/PXHD).

The GMCH also increases the main memory interface bandwidth and maximum memory

configuration with a 72-bit wide memory interface.

The GMCH integrates the following main functions:

An integrated high performance main memory subsystem.