SE7221BK1-E Technical Product Specification

Revision 1.3

14

4.2.1.6 Wake-up Control

The Super IO contains functionality that allows various events to control the power-on and

power-off the system.

4.2.2 BIOS Flash

The board incorporates an Intel®

®

28F320C3 flash memory component. The 28F320C3 is a

high-performance 32-megabit memory component that provides 2096K x 16 of BIOS and non-

volatile storage space. The flash device is connected through the X Bus from Super IO.

4.2.3 System Health Support

I2C interface to LM96000 sensors

Fan Monitor and Control (FMC)

— One PWM-based fan controls

— Software or local temperature feedback control

Chassis intrusion detection

5. I/O Subsystem

5.1 PCI Subsystem

The primary I/O buses for the SE7221BK1-E are 3 independent PCI bus segments (4

independent segments with SE7221BK1LX sku) with PCI, PCI-E and two PCI-X buses. The PCI

buses comply with the PCI Local Bus Specification, Rev 2.3. The P32-A bus segment is

directed through the ICH6R. The P32-B and P64-C bus segment are independently configured

to PXH that is through ICH6R by PCI Express* x 4 interface. The PCI-E x8 bus is directed

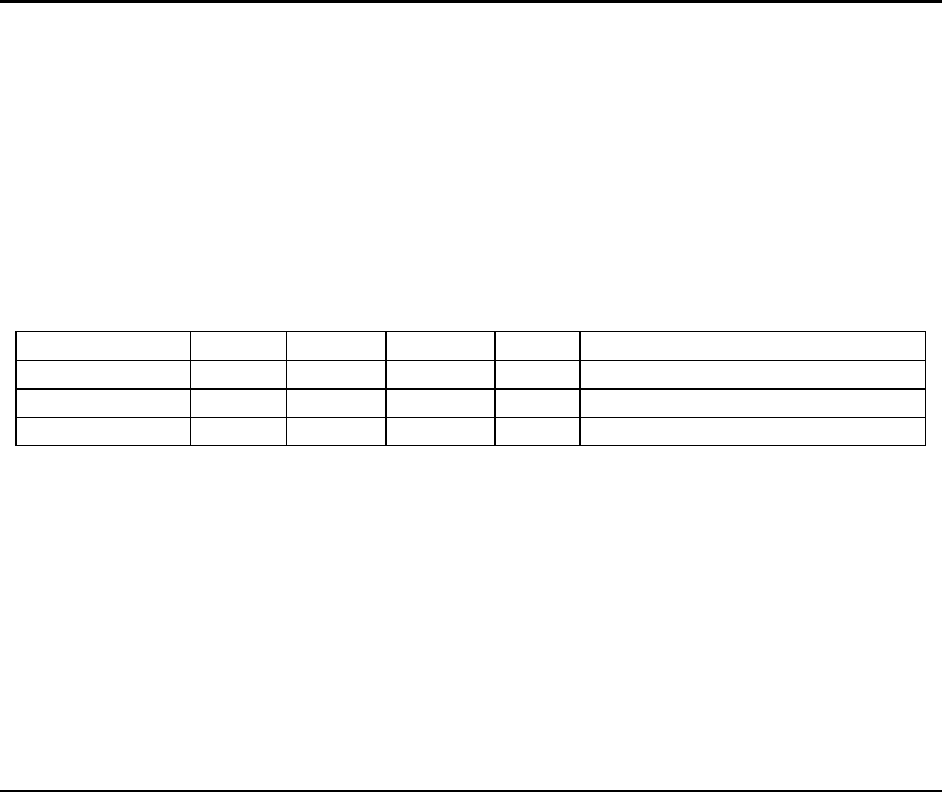

through the GMCH. The table below lists the characteristics of the three PCI bus segments.

Table 5. PCI Bus Segment Characteristics

PCI Bus Segment Voltage Width Speed Type PCI I/O Card Slots

PCI 5V 32 bits 33MHz P32-A Slot 1

PCI-X 3.3V 64 bits 66/100MHz P64-C Slot 4; Slot 5, (Slot 6 through riser card)

PCI-E (x8) 3.3V 8 lanes 100MHz Slot 6

5.1.1 P32-A: 32-bit/33-MHz PCI Subsystem

All 32-bit/33-MHz PCI I/O for the board is directed through the ICH6R. The 32-bit/33-MHz PCI

segment created by the ICH6R is known as the P32-A segment. The P32-A segment supports

the following embedded devices and connectors:

One 10/100/1000-T Network Interface Controller: Intel® 82541PI Fast Ethernet

Controller.

5.1.1.1 Device IDs (IDSEL)

Each device under the PCI hub bridge has its IDSEL signal connected to one bit of AD [31:16],

which acts as a chip select on the PCI bus segment in configuration cycles. This determines a