SE7221BK1-E Technical Product Specification

19

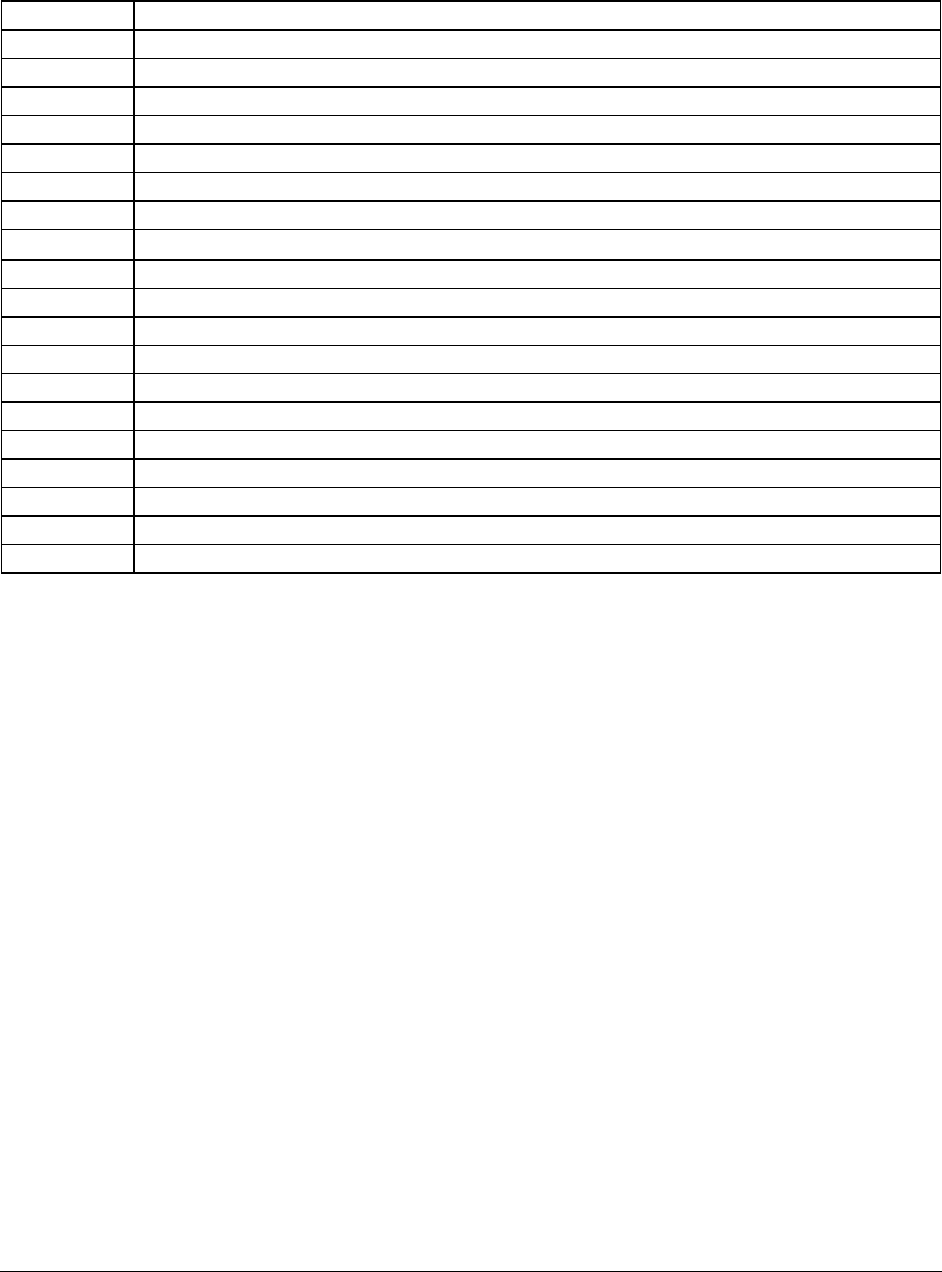

Table 14. Interrupt Definitions

ISA Interrupt Description

INTR Processor interrupt.

NMI NMI to processor.

IRQ0 System timer

IRQ1 Keyboard interrupt.

IRQ2 Slave PIC

IRQ3 Serial port 1 or 2 interrupt from SUPER IO device, user-configurable.

IRQ4 Serial port 1 or 2 interrupt from SUPER IO device, user-configurable.

IRQ5

IRQ6 Floppy disk.

IRQ7 Parallel Port / Generic

IRQ8_L Active low RTC interrupt.

IRQ9 SCI*

IRQ10 Generic

IRQ11 Generic

IRQ12 Mouse interrupt.

IRQ13 Floaty processor.

IRQ14 Compatibility IDE interrupt from primary channel IDE devices 0 and 1.

IRQ15 Secondary IDE Cable

SMI* System Management Interrupt. General purpose indicator sourced by the ICH6R to the processors.

5.4.3 Serialized IRQ Support

The SE7221BK1-E server board supports a serialized interrupt delivery mechanism. Serialized

Interrupt Requests (SERIRQ) consists of a start frame, a minimum of 17 IRQ / data channels,

and a stop frame. Any slave device in the quiet mode may initiate the start frame. While in the

continuous mode, the start frame is initiated by the host controller.

5.5 PCI Error Handling

The PCI bus defines two error pins, PERR# and SERR#, for reporting PCI parity errors and

system errors, respectively. In the case of PERR#, the PCI bus master has the option to retry

the offending transaction, or to report it using SERR#. All other PCI-related errors are reported

by SERR#. SERR# is routed to NMI if enabled by BIOS.