USB-1616HS-2 User's Guide Functional Details

27

When reading synchronously, all counters are set to zero at the start of an acquisition. When reading

asynchronously, counters may be cleared on each read, count up continually, or count until the 16-bit or 32-bit

limit has been reached. See counter mode explanations below.

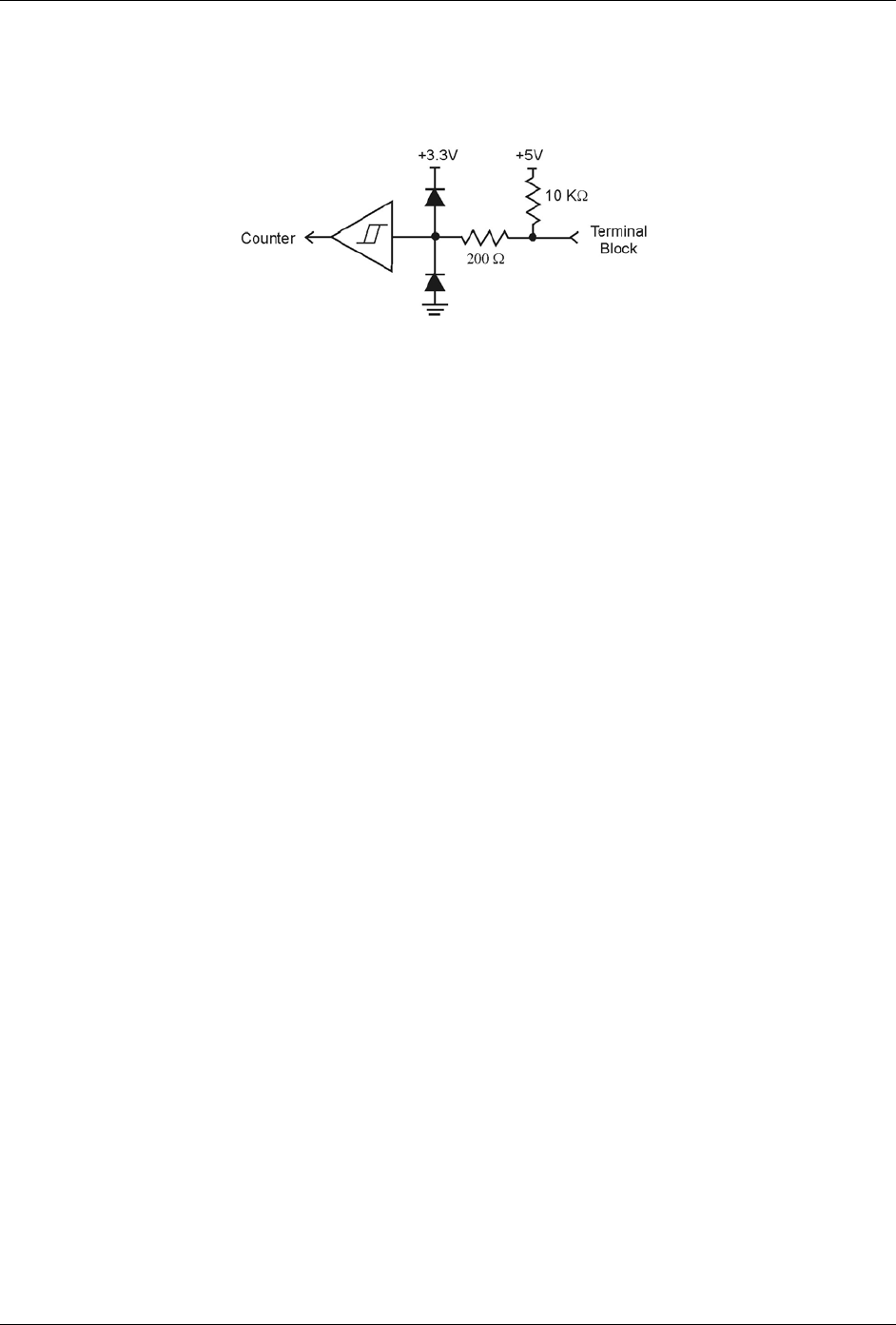

Figure 12. Typical USB-1616HS-2 counter channel

Tips for making high-speed counter measurements (> 1 MHz)

Use coax or twisted-pair wire. Connect one side to Digital Common.

If the frequency source is tolerant, parallel-terminate the coax or twisted-pair with a 50 or 100 resistor

at the terminal block.

The amplitude of the driving waveform should be as high as possible without violating the over-voltage

specification.

To ensure adequate switching, waveforms should swing at least 0 V to 5 V and have a high slew rate.

Mapped channels

A mapped channel is one of four counter input signals that can get multiplexed into a counter module. The

mapped channel can participate with the counter's input signal by gating the counter, latching the counter, and

so on. The four possible choices for the mapped channel are the four counter input signals (post-debounce).

A mapped channel can be used to:

gate the counter

decrement the counter

latch the current count to the count register

Usually, all counter outputs are latched at the beginning of each scan within the acquisition. However, you can

use a second mapped channel to latch the counter output.

Counter modes

A counter can be asynchronously read with or without clear on read. The asynchronous read-signals strobe

when the lower 16-bits of the counter are read by software. The software can read the counter's high 16-bits

some time later after reading the lower 16-bits. The full 32-bit result reflects the timing of the first

asynchronous read strobe.

Totalize mode

The Totalize mode allows basic use of a 32-bit counter. While in this mode, the channel's input can only

increment the counter upward. When used as a 16-bit counter (counter low), one channel can be scanned at the

12 MHz rate. When used as a 32-bit counter (counter high), two sample times are used to return the full 32-bit

result. Therefore a 32-bit counter can only be sampled at a 6 MHz maximum rate. If you only want the upper

16 bits of a 32-bit counter, then you can acquire that upper word at the 12 MHz rate.

The counter counts up and does not clear on every new sample. However, it does clear at the start of a new scan

command.