38

!

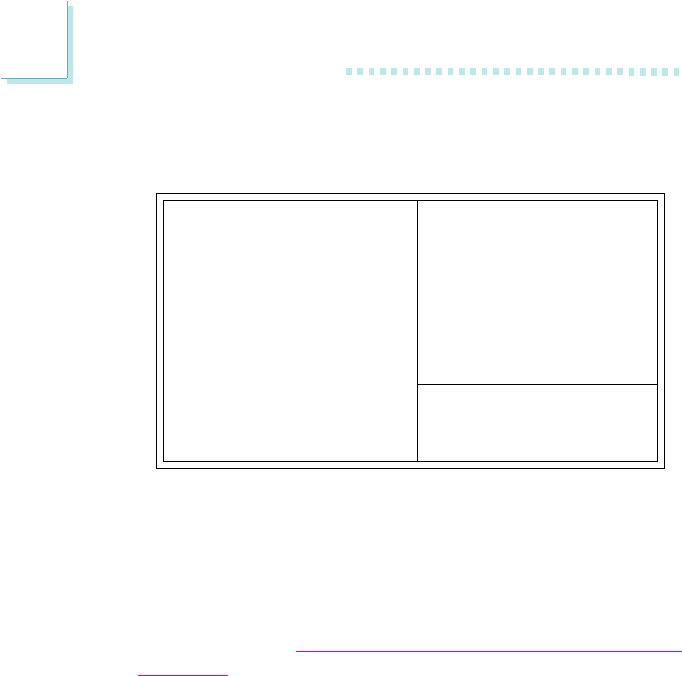

Award BIOS Setup Utility

3.1.3 Chipset Features Setup

:3

:3

:3

: Disabled

: Non-ECC

: Disabled

: Disabled

: Disabled

:1

:1

: Disabled

: Disabled

:64

: Default

: Disabled

ROM PCI/ISA BIOS

CHIPSET FEATURES SETUP

AWARD SOFTWARE, INC.

SDRAM RAS-to-CAS Delay

SDRAM RAS Precharge Time

SDRAM CAS Latency Time

SDRAM Precharge Control

DRAM Data Integrity Mode

System BIOS Cacheable

Video BIOS Cacheable

Video RAM Cacheable

8 Bit I/O Recovery Time

16 Bit I/O Recovery Time

Memory Hole At 15M-16M

PCI 2.1 Compliance

AGP Aperture Size (MB)

CPU/PCI Clock (MHz)

Spread Spectrum

↑ ↓ → ←

ESC

F1

F5

F6

F7

: Quit

: Help

: Old Values

: Load Fail-Safe Settings

: Load Optimal Settings

PU/PD/+/-

(Shift) F2

: Select Item

: Modify

: Color

The settings on the screen are for reference only. Your version may not be

identical to this one.

This section gives you functions to configure the system based on

the specific features of the chipset. The chipset manages bus

speeds and access to system memory resources. It also

coordinates communications between the conventional ISA bus

and the PCI bus. These items should not be altered unless

necessary. The default settings have been chosen because they

provide the best operating conditions for your system. The only

time you might consider making any changes would be if you

discovered some incompatibility or that data was being lost while

using your system.

SDRAM RAS-to-CAS Delay

This field allows you to insert a timing delay between the CAS and

RAS strobe signals, used when DRAM is written to, read from, or

refreshed. This field applies only when synchronous DRAM is

installed in the system.

SDRAM RAS Precharge Time

If there is insufficient number of cycles for the RAS to accumulate

its charge before DRAM refresh, the refresh may be incomplete and

the DRAM may fail to retain data.