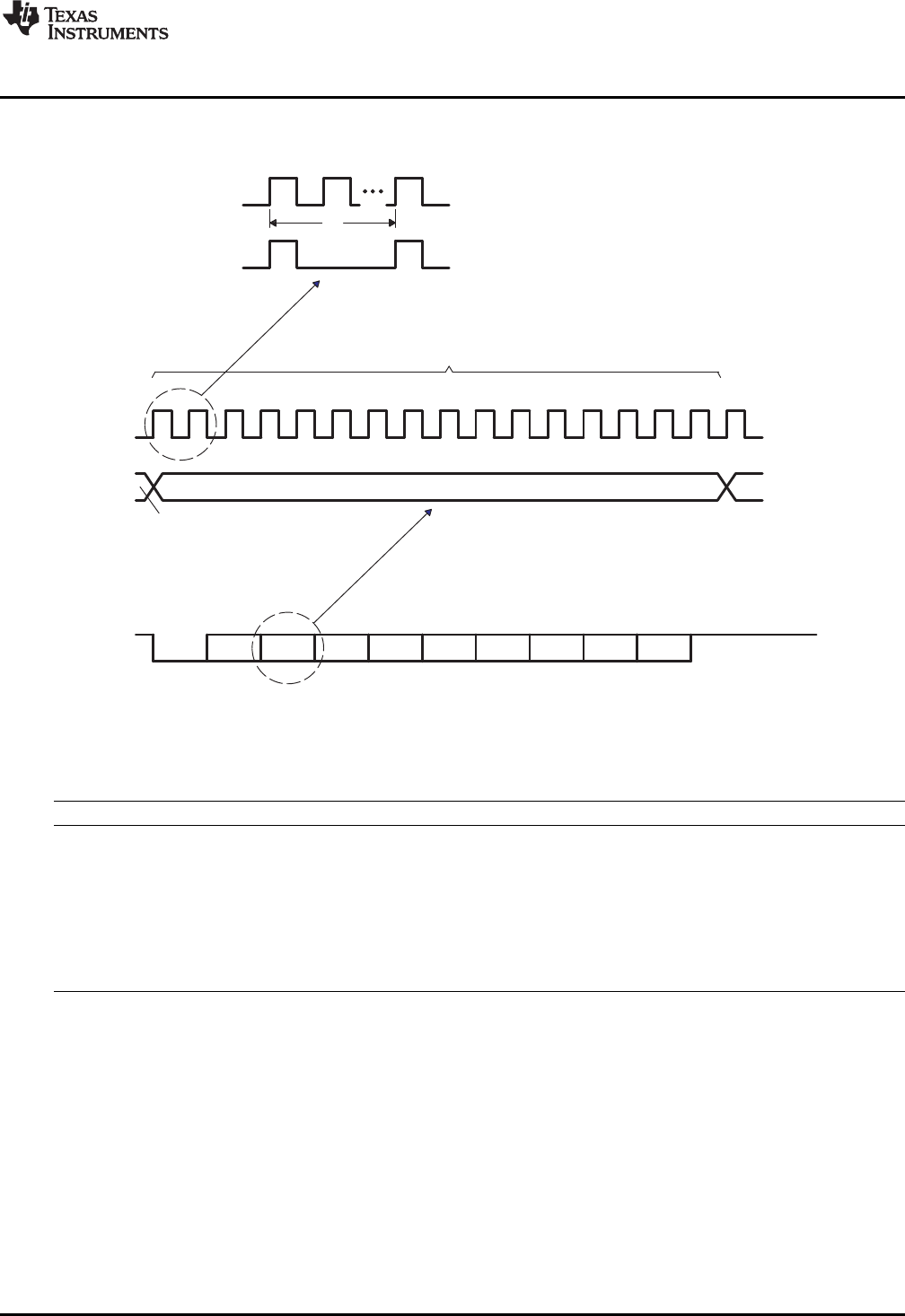

BCLK

Each bit lasts 16 BCLK cycles.

When receiving, the UART samples the bit in the 8th cycle.

D0

TX,

RX

D1 D2

PARITY

D7D6D5

STOP2STOP1

D1 D4D2 D3

START

D0

TX,

RX

UART input clock

n UART input clock cycles, where n = divisor in DLH:DLL

n

BCLK

www.ti.com

Peripheral Architecture

Figure 3. Relationships Between Data Bit, BCLK, and UART Input Clock

Table 2. Baud Rate Examples for 27 MHz UART Input Clock

Baud Rate Divisor Value Actual Baud Rate Error (%)

2400 703 2400.427 0.018

4800 352 4794.034 -0.124

9600 176 9588.068 -0.124

19200 88 19176.14 -0.124

38400 44 38352.27 -0.124

56000 30 56250 0.446

128000 13 129807.7 1.412

11

SPRU997C–December 2009 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2009, Texas Instruments Incorporated